DRAFT REPORT

# Energy Efficiency Scaling for Two Decades Research and Development Roadmap

Version 1.0

August 2024

## Disclaimer

This work was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors or their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or any third party's use or the results of such use of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof or its contractors or subcontractors. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof, its contractors or subcontractors.

## Authors

The initial draft of this report was prepared by Energetics, Inc., for the U.S. Department of Energy Office of Energy Efficiency and Renewable Energy, Advanced Materials and Manufacturing Technologies Office (AMMTO) based on inputs from a year-long roadmapping effort involving the participating organizations below documented at <https://live-slac-microelectronics-d9.pantheonsite.io/sustainable-computing/energy-efficient-and-sustainable-computing>.

The primary AMMTO author and Energy Efficiency Scaling for Two Decades (EES2) lead is Tina Kaarsberg, AMMTO.

The primary EES2 analysis lead and author is Sadasivan Shankar, SLAC National Accelerator Laboratory.

The primary Energetics, Inc., authors of this report are I-Hsi Daniel Lu, Nick R. Johnson, Kenta Shimizu, Emmanuel Taylor, Russ Jones, Harper Alerion, and Ken Weaver.

The authors acknowledge Matt Roney, Dwight Tanner, and Jessica Blackburn from AMMTO's technical writing team who provided invaluable editorial support.

They also acknowledge Thomas Finamore, the Energetics, Inc., producer who provided graphic editorial support.

# Participating Organizations<sup>1</sup>

## Government

U.S. Department of Energy AMMTO

U.S. Department of Commerce National Institute of Standards and Technology

## National Laboratories

Argonne National Laboratory

Brookhaven National Laboratory

Fermi National Laboratory

Lawrence Berkeley National Laboratory

Lawrence Livermore National Laboratory

National Renewable Energy Laboratory

Oak Ridge National Laboratory

Pacific Northwest National Laboratory

Sandia National Laboratories

SLAC National Accelerator Laboratory

## Industry

3D Epitaxial Technologies

Finwave Semiconductor

Multi3D

Advanced Micro Devices

General Electric Vernova

NanoSonic Inc.

Aligned Carbon

Google Great Lake Crystal Technologies

Nantero

America's Frontier Fund

Hyperion

Nhanced Semiconductors, Inc

America's Frontier Fund

IBM

Paragrapf

Applied Materials

IEEE- USA

PseudolithIC

ARM

Infineon Technologies

Quantum Silicon

BRDG Bridge to Connect

Intel

Radiation Monitoring Devices, Inc.

Cadence

Iris Light

SAP

Carbice

Liquid

SEMI

Carbon Technology, Inc.

Metis Microsystems

Semiconductor Research Corporation

Dedalo AI

Micron Technology

Siemens

Dexmat

Microsoft

Energetics

<sup>1</sup> Except for the National Institute of Science and Technology, all participants' organizations have formally signed the EES2 pledge.

Sixline Semiconductor

Tetramer

Wolley Tech

Synopsys

Tiptek

Zyvex Labs

TechSearch International

VIEE

Universities

Duke University

Florida Semiconductor Institute

Hasso Plattner Institute

Los Angeles Trade-Technical College

Stony Brook University

University of Colorado at Boulder

University of Nebraska at Lincoln

University of Texas at Dallas

University of Texas at San Antonio

## Working Group Co-Chairs

### Algorithms and Software

Brian Hirano, Micron Technology

Tapan Shah, General Electric Vernova

### Advanced Packaging and Heterogeneous Integration

Moinuddin Ahmed, Argonne National Laboratory

Na Li, Carbice

### Circuits and Architectures

Azeez Bhavnagarwala, Metis Microsystems

Emre Salman, Stony Brook University

### Education and Workforce Development

Russell Harrison, IEEE-USA

David Shahoulian, Intel

### Manufacturing Efficiency and Environmental Sustainability

Josh Ballard, Zyvex Labs

Prashant Nagapurkar, Oak Ridge National Laboratory

Steve Putna, Texas A&M University

### Materials and Devices

Jayasimha Atulasimha, Virginia Commonwealth University

John Baniecki, SLAC National Accelerator Laboratory

Paul Fischer, Intel

Shashank Misra, Sandia National Laboratories

### **Metrology and Benchmarking**

Craig Green, Carbice

James Booth, National Institute of Science and Technology

### **Power and Control Electronics**

Paul Sharps, Sandia National Laboratories

Tim McDonald, Infineon Technologies

## **Acknowledgments**

The authors would like to acknowledge the additional significant contributions of the following working group members and Energetics staff members:

|                                                       |                                                          |                                                |

|-------------------------------------------------------|----------------------------------------------------------|------------------------------------------------|

| Aaron Fisher, Lawrence Livermore National Laboratory  | Caecilia Gotama, BRDG                                    | Elizabeth Neville Reyes, Applied Materials     |

| Alexander Paramonov, Argonne National Laboratory      | Can Bayram, University of Illinois                       | Eungsan Cho, Infineon Technologies             |

| Amanda Petford-Long, Argonne National Laboratory      | Carlos Gutierrez, Sandia National Laboratories           | Francesco Musso, Dedalo AI                     |

| Amir Ziabari, Oak Ridge National Laboratory           | Chad Husko, Iris Light                                   | Godwin Maben, Synopsys                         |

| Angel Yanguas-Gil, Argonne National Laboratory        | Conrad James, Sandia National Laboratories               | Hal Finkel, DOE/ASCR                           |

| Anil Mane, Argonne National Laboratory                | Dan Green, PseudolithIC                                  | Harish Bhandari, RMDI                          |

| Antonino Tumeo, Pacific Northwest National Laboratory | Daniel Gopman, NIST                                      | Hsien-Hsin Sean Lee, Intel                     |

| Ashfia Huq, Sandia National Laboratories              | Danny Clavette, Infineon Technologies                    | Hyunim Chung, Sandia National Laboratory       |

| Ben Tang, Infineon Technologies                       | David Gilmer, Nantero                                    | Jack Kotovsky, Lawrence Livermore National Lab |

| Bill Gervasi, Nantero                                 | David Gothold, Pacific Northwest National Laboratory     | James Provine, Aligned Carbon                  |

| Brian Rowden, Oak Ridge National Laboratory           | David Voss, Energetics                                   | Jan Vardaman, TechSearch International         |

|                                                       | Dhanushkodidurai Mariappan, GE Vernova                   | Jigesh Patel, Synopsys                         |

|                                                       | Dhireesha Kudithipudi, University of Texas - San Antonio | Jo Luo, Nantero                                |

|                                                       |                                                          | Joe Kline, NIST                                |

|                                                     |                                                    |                                                    |

|-----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|

| Joel Varley, Lawrence Livermore National Laboratory | Percy Kawas, Infineon Technologies                 | Steffen McKernan, Carbon Technology                |

| John Leung, Intel                                   | Peter Dowben, University of Nebraska - Lincoln     | Steve Buffat, Nantero                              |

| Josh Fryman, Intel                                  | Petr Sushko, Pacific Northwest National Laboratory | Steve Pawlowski, Micron                            |

| Julia Deitz, Sandia National Laboratories           | Radislav Potyrailo, GE Vernova                     | Sushanta Pal, Nantero                              |

| Keita Teranishi, Oak Ridge National Laboratory      | Rahul Sen, Nantero                                 | Timothy Wei, University of Nebraska-Lincoln        |

| Keith Lanier, Synopsys                              | Ricardo Ruiz, Berkeley Lab                         | Tommy Finamore, Energetics                         |

| Maria DiGiulian, Infineon Technologies              | Richard Kainradl, SAP                              | Victor Zhirnov, Semiconductor Research Corporation |

| Martin Frank, IBM                                   | Rick Ridgley, Nantero                              | Vishal Saxena, University of Delaware              |

| Matthew Weimer, Forge Nano                          | Sam Salama, Hyperion                               | Volker Sorger, University of Florida               |

| May Gokhale, Lawrence Livermore National Lab        | Sameh Khalil, Infineon Technologies                | Walt Zalis, Energetics                             |

| Muralidharan Govindarajan, Oak Ridge National Lab   | Sean Shaheen, University of Colorado - Boulder     | Wayne Johnson, ICF                                 |

| Nick Lalena, DOE                                    | Shari Liss, SEMI Foundation                        | Wiley Kirk, 3DET                                   |

| Pamela Klabbers, Fermilab                           | Srilatha Manne, AMD                                | Yiran Chen, Duke University                        |

|                                                     |                                                    | Yuepeng Zhang, Argonne National Laboratory.        |

## List of Abbreviations

|         |                                                 |

|---------|-------------------------------------------------|

| 3DHI    | 3-dimensional heterogeneous integration         |

| AC      | Alternating current                             |

| ADK     | Assembly design kit                             |

| AI      | Artificial intelligence                         |

| ALU     | Arithmetic logic unit                           |

| AMD     | Advanced Micro Devices                          |

| ANL     | Argonne National Laboratory                     |

| ANN     | Artificial neural network                       |

| AP      | Advanced packaging                              |

| APHI    | Advanced packaging/heterogeneous integration    |

| ASIC    | Application-specific integrated circuit         |

| AST     | Abstract syntax tree                            |

| BEOL    | Back-end-of-line                                |

| CAD     | Computer-aided design                           |

| CDO     | Carbon-doped silicon oxide                      |

| CDR     | Clock and data recovery                         |

| CD-SAXS | Critical-dimension small-angle X-ray scattering |

| CD-SEM  | Critical-dimension scanning electron microscope |

| CIM     | Compute-in-memory                               |

| CISC    | Complex instruction set computer                |

| CMOS    | Complementary metal–oxide–semiconductor         |

| CMP     | Chemical mechanical polishing                   |

| CNT     | Carbon nanotube                                 |

| CNTFET  | Carbon nanotube field-effect transistor         |

| CPO     | Co-packaged optics                              |

| CPU     | Central processing unit                         |

| Cu      | Copper                                          |

| CVD     | Chemical vapor deposition                       |

| CXL     | Compute express link                            |

| D2W     | Die-to-wafer                                    |

| DBI     | Direct bond interconnect                        |

|        |                                           |

|--------|-------------------------------------------|

| DC     | Direct current                            |

| DDR    | Double data rate                          |

| DFT    | Density functional theory                 |

| DNN    | Deep neural network                       |

| DoD    | Department of Defense                     |

| DOE    | U.S. Department of Energy                 |

| DRAM   | Dynamic random-access memory              |

| DSA    | Domain-specific architecture              |

| DSL    | Domain-specific language                  |

| DTCO   | Design technology co-optimization         |

| DTM    | Dynamic thermal management                |

| EAM    | Electro-absorption modulator              |

| EDA    | Electronic design automation              |

| EES2   | Energy Efficiency Scaling for Two Decades |

| EMI    | Electro-migration issues                  |

| EMIB   | Embedded multi-die interconnect bridge    |

| EOM    | Electro-optic modulator                   |

| ESD    | Electrostatic discharge                   |

| FeFET  | Ferroelectric field-effect transistor     |

| FEOL   | Front end of line                         |

| FET    | Field-effect transistor                   |

| FinFET | Fin field-effect transistor               |

| FMEA   | Failure mode effect analysis              |

| FP16   | Floating point 16 (16-bit representation) |

| FP32   | Floating point 32 (32-bit representation) |

| FPGA   | Field programmable gate array             |

| FSG    | Fluorosilicate glass                      |

| FTJ    | Ferroelectric tunnel junction             |

| GDDR   | Graphics double data rate                 |

| GPU    | Graphics processing unit                  |

| GWP    | Gross World Product                       |

| HBM    | High bandwidth memory                     |

|                  |                                                   |

|------------------|---------------------------------------------------|

| HCl              | Hydrochloric acid                                 |

| HDI              | High-density interconnects                        |

| HDI              | Hydrogen Deficiency Index                         |

| HF               | Hydrofluoric acid                                 |

| HI               | Heterogeneous integration                         |

| HIST             | Heterogeneous interconnect stitching technology   |

| HMC              | Hybrid memory cube                                |

| HNO <sub>3</sub> | Nitric acid                                       |

| HPC              | High-performance computing                        |

| HVAC             | Heating, ventilation, and air conditioning        |

| HVM              | High-volume manufacturing                         |

| I/O              | Input/output                                      |

| IC               | Integrated circuit                                |

| IC               | Interconnect                                      |

| ICT              | Information and communication technology          |

| IEEE             | Institute of Electrical and Electronics Engineers |

| ILD              | Interlayer dielectric                             |

| IMEC             | Interuniversity Microelectronics Centre           |

| InP              | Indium phosphide                                  |

| Int32            | Integer 32 (32-bit precision)                     |

| Int8             | Integer 8 (8-bit precision)                       |

| IoT              | Internet of Things                                |

| IP               | Intellectual property                             |

| Ir               | Iridium                                           |

| IRDS             | International Roadmap for Devices and Systems     |

| ISA              | Instruction set architecture                      |

| JVM              | Java Virtual Machine                              |

| KOH              | Potassium hydroxide                               |

| LED              | Light-emitting diode                              |

| LMP              | Liquid metal paste                                |

| LPDDR            | Low-power double data rate                        |

| MAC              | Multiply-accumulate                               |

|        |                                                      |

|--------|------------------------------------------------------|

| MAPT   | Microelectronics and Advanced Packaging Technologies |

| MBE    | Molecular-beam epitaxy                               |

| MIEC   | Mixed ion-electric conductor                         |

| MIV    | Monolithic inter-tier via                            |

| ML     | Machine learning                                     |

| MLIR   | Multi-level intermediate representation              |

| MOCVD  | Metalorganic chemical vapor deposition               |

| MOSFET | Metal–oxide–semiconductor field-effect transistor    |

| MWNT   | Multi-walled carbon nanotube                         |

| MZM    | Mach-Zehnder modulator                               |

| NAND   | Not AND memory                                       |

| NaOH   | Sodium hydroxide                                     |

| NASA   | National Aeronautics and Space Agency                |

| NDE    | Non-destructive evaluation                           |

| NIST   | National Institute of Standards and Technology       |

| NRAM   | Nanotube random-access memory                        |

| NRAM   | Non-volatile random-access memory                    |

| NVM    | Non-volatile memory                                  |

| OEM    | Original equipment manufacturer                      |

| OOK    | On/off keying                                        |

| ORNL   | Oak Ridge National Laboratory                        |

| OSAT   | Outsourced semiconductor assembly and test companies |

| OSC    | Organic semiconductor                                |

| PACE   | Power and control electronics                        |

| PAM4   | Pulse amplitude modulation 4-level                   |

| PCB    | Printed circuit board                                |

| PCIe   | Peripheral Component Interconnect Express            |

| PCRAM  | Phase change random-access memory                    |

| PDK    | Process design kit                                   |

| PDU    | Power distribution unit                              |

| PFC    | Power factor correction                              |

| PIM    | Process-in-memory                                    |

|                                |                                                     |

|--------------------------------|-----------------------------------------------------|

| PINN                           | Physics-informed neural network                     |

| pJ                             | Picojoule                                           |

| PUE                            | Power use effectiveness                             |

| QD                             | Quantum dot                                         |

| QW                             | Quantum well                                        |

| RC                             | Resistive-capacitive                                |

| R&D                            | Research and development                            |

| RD&D                           | Research, development, and demonstration            |

| RDL                            | Redistribution layer                                |

| ReRAM                          | Resistive random-access memory                      |

| RF                             | Radio frequency                                     |

| Rh                             | Rhodium                                             |

| RISC-V                         | Reduced instruction set computer 5                  |

| RM                             | Ring modulator                                      |

| Ru                             | Ruthenium                                           |

| SerDes                         | Serializer/deserializer                             |

| Sandia                         | Sandia National Laboratories                        |

| SIA                            | Semiconductor Industry Association                  |

| SiC                            | Silicon carbide                                     |

| SiCN                           | Silicon carbon nitride                              |

| SiGAA                          | Silicon gate-all-around                             |

| SiGe                           | Silicon germanium                                   |

| SiO <sub>2</sub>               | Silicon dioxide                                     |

| SiP                            | System in package                                   |

| Si <sub>x</sub> N <sub>y</sub> | Silicon nitride                                     |

| SLAC                           | Stanford Linear Accelerator Center                  |

| SNN                            | Spike neural network                                |

| SNR                            | Signal-to-noise ratio                               |

| SOA                            | Semiconductor optical amplifier                     |

| SoC                            | System on Chip                                      |

| SOIC                           | Small outline integrated circuit                    |

| SOI-TFET                       | Silicon-on-insulator tunnel field-effect transistor |

|        |                                                   |

|--------|---------------------------------------------------|

| SOP    | Small outline package                             |

| SRAM   | Static random-access memory                       |

| SRC    | Semiconductor Research Corporation                |

| SSD    | Solid state drive                                 |

| STCO   | System technology co-optimization                 |

| STEM   | Science, technology, engineering, and mathematics |

| STTRAM | Spin transfer torque random-access memory         |

| SWNT   | Single-walled carbon nanotube                     |

| TCB    | Thermocompression bonding                         |

| TCO    | Total cost of ownership                           |

| TEM    | Transmission electron microscopy                  |

| TFET   | Tunnel field-effect transistor                    |

| TIM    | Thermal interface material                        |

| TMDC   | Transition-metal dichalcogenide                   |

| TPU    | Tensor processing unit                            |

| TRL    | Technology readiness level                        |

| TSMC   | Taiwan Semiconductor Manufacturing Company        |

| TSV    | Through silicon via                               |

| UCle   | Universal Chiplet Interconnect Express            |

| UMC    | United Microelectronics Corporation               |

| UPS    | Uninterruptible power supply                      |

| VCache | Vertical cache memory                             |

| W2W    | Wafer-to-wafer                                    |

| WDM    | Wavelength division multiplexing                  |

## Executive Summary

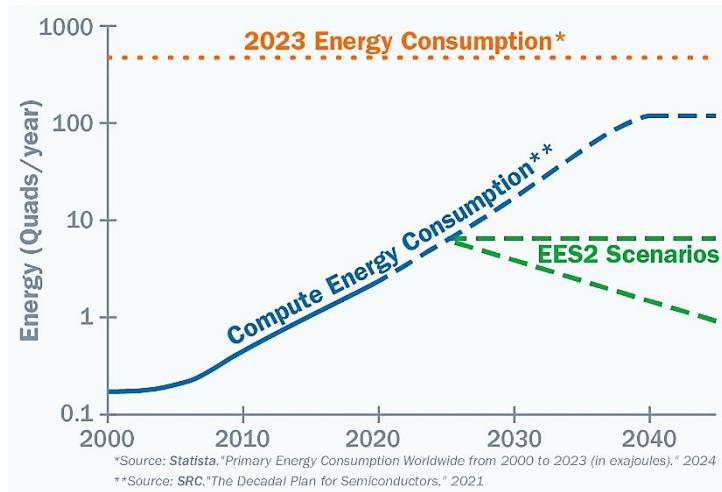

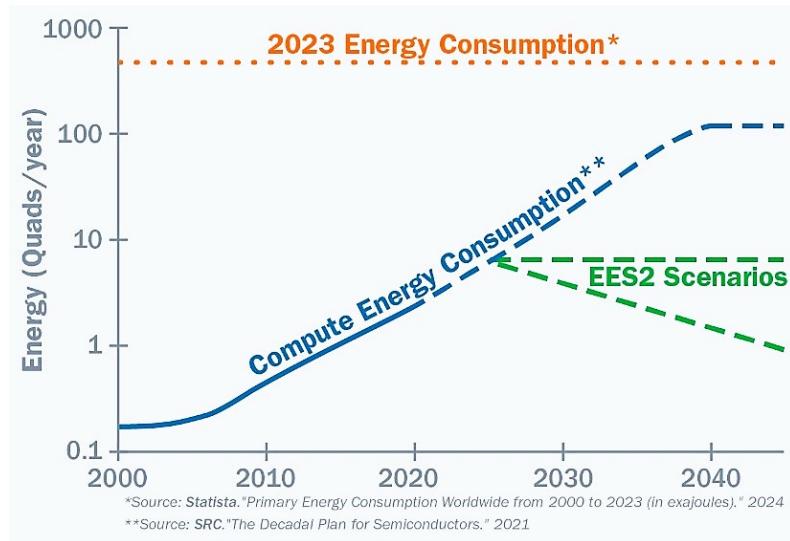

This R&D roadmap is part of the U.S. Department of Energy's (DOE's) pledge to increase microelectronics' energy efficiency 1,000-fold in two decades. With rapidly emerging challenges such as the increase in electricity use of data centers, innovations that exponentially increase energy efficiency are urgently needed to put microelectronics' electricity use on a more sustainable path (see Figure ES-1). Just as President Kennedy did with his moonshot goal 60 years ago, DOE pledged to achieve this energy efficiency goal not because it is easy but because it is hard.

### Background

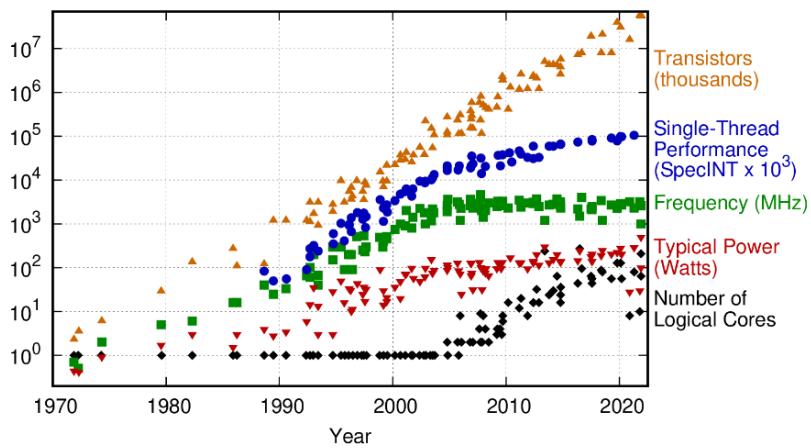

Since the invention of the integrated circuit or "chip" 65 years ago, semiconductor-based electronics, or microelectronics, have enabled growth of information technology (IT)—computing, communication, and other electronics applications. Chip manufacturers now layer billions of semiconductor-based switches (i.e., transistors, the foundational unit of electronic devices) onto silicon to make the microelectronics that are essential for modern life. IT growth in the last century was propelled forward by the biennial doubling of transistor density on chips, which led to greater performance and lower cost per function. This tradition of exponential performance improvements is why much of the semiconductor industry already sets exponential technical goals. For example, the initial pledge signer, Advanced Micro Devices (AMD), had already set the goal to increase the efficiency of its chips 30 times by 2025; since signing DOE's pledge, AMD has increased its goal to 100 times by 2027.

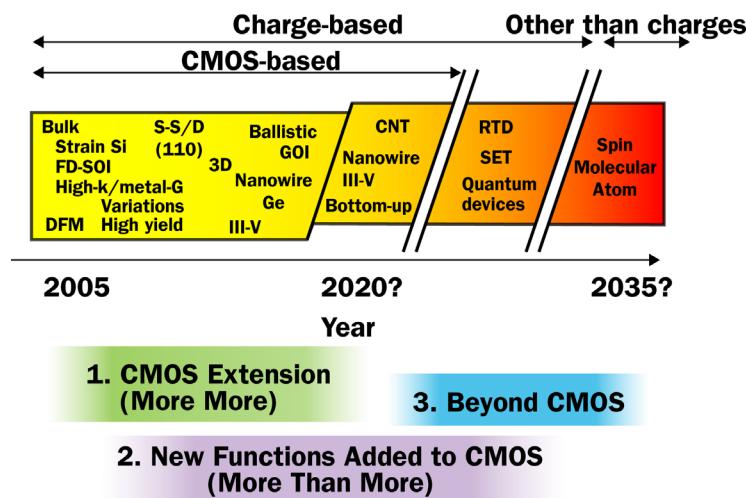

As transistors were miniaturized, chip power density initially remained constant (Dennard scaling), leading to more than doubling energy efficiency biennially. By 2005, however, this biennial efficiency doubling began to slow markedly as it reached certain physical limits. The slowing of efficiency doubling coupled with the rapid rise in energy and computation-intensive IT applications, has led to sharp increases in global IT energy consumption. According to the Semiconductor Research Corporation (SRC), by 2010, global computing energy use began to double every 3 years.

Figure ES 1. SRC energy consumption forecast and the EES2 efficiency goal in two energy consumption scenarios

### Energy Efficiency Scaling for Two Decades

The U.S. Department of Energy's Advanced Materials and Manufacturing Technologies Office (AMMTO) launched a national initiative with industry partners, national labs, and academia, called Energy Efficiency Scaling for Two Decades (EES2) in 2022. This ambitious program aims to double the energy efficiency of microelectronics biennially, targeting a 1,000-fold

improvement over two decades. A key component of EES2 is this version 1.0 roadmap, the first in a series of research, demonstration, and demonstration (RD&D) roadmaps. This document is a product of extensive literature review and energy analysis, collaboration meetings between nine working groups, and expert input during the writing process. The working groups met monthly, with the organizing committee engaging in literature review and analysis to prepare for the following meeting.

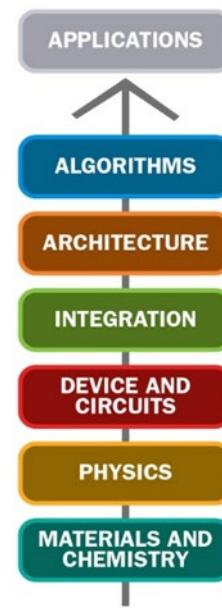

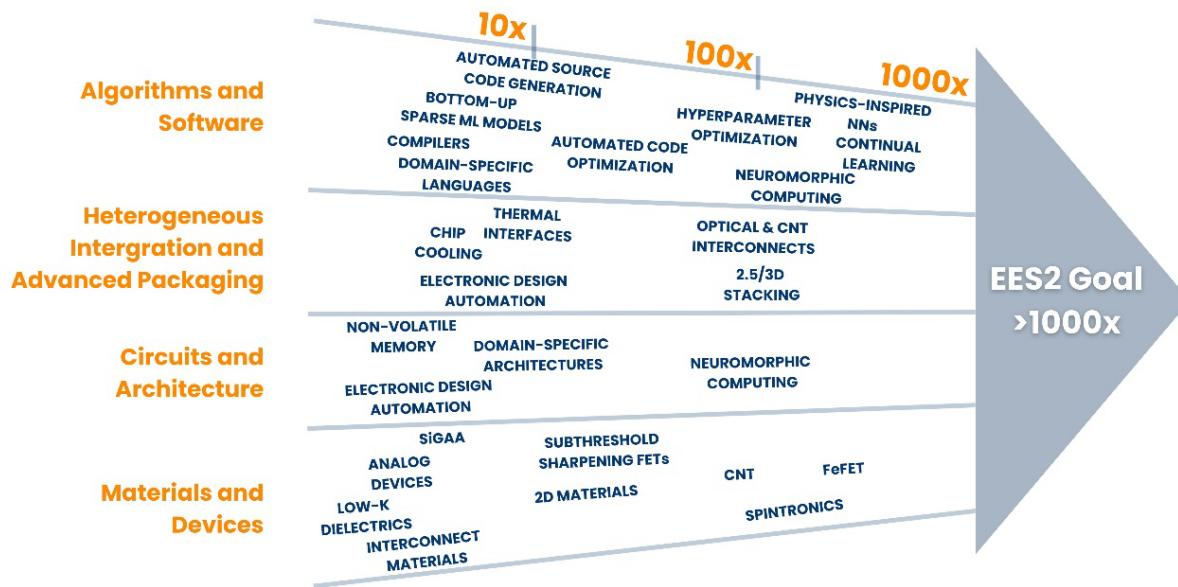

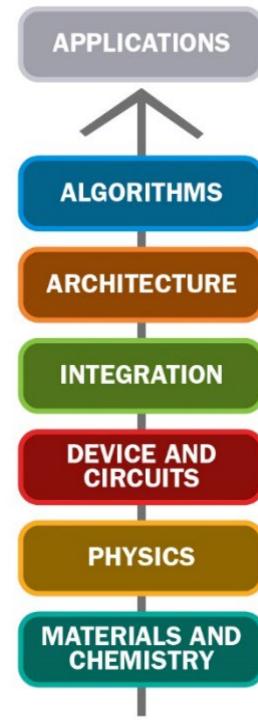

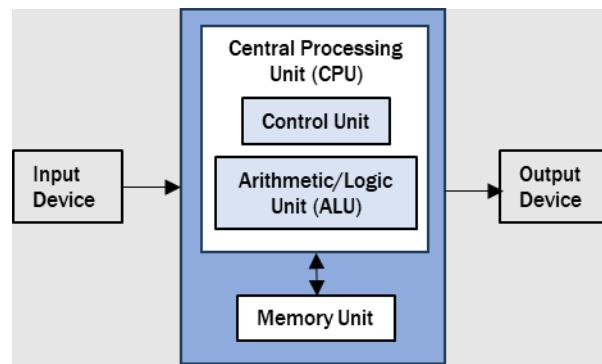

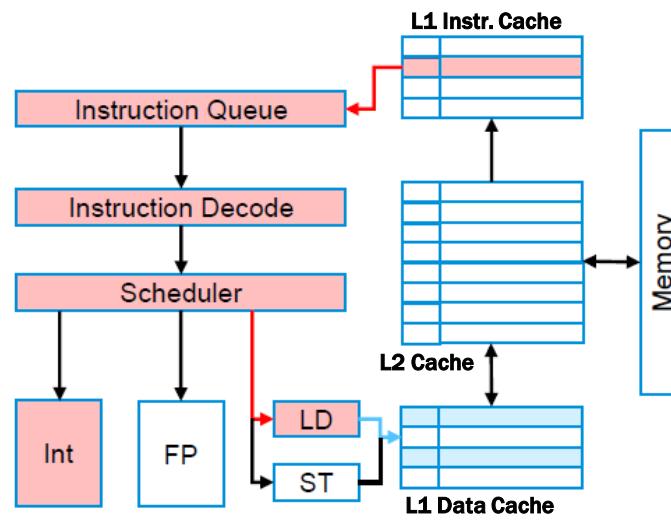

The EES2 roadmap focuses on the largest and fastest growing IT energy user, the “compute stack” (see Figure ES-2), which comprises everything from devices to software. The stack shown is from the seminal DOE report *Basic Research Needs for Microelectronics* (DOE Office of Science, 2018), which extended the notion of co-design from simply designing hardware and software together to specifically co-designing adjacent layers of the hardware with adjacent layers of the software. This roadmap examines innovative technologies co-designed by experts on different parts of the stack that can exponentially increase computing energy efficiency. This roadmap is a first step in a multi-year research effort to develop and deploy portfolios of cutting-edge microelectronics technologies that are 10-, 100-, and even 1,000-times more energy efficient than the technologies they replace. Alone, none of the technologies will achieve the industry-wide biennial efficiency doubling leading to the 21 1,000-times goal.

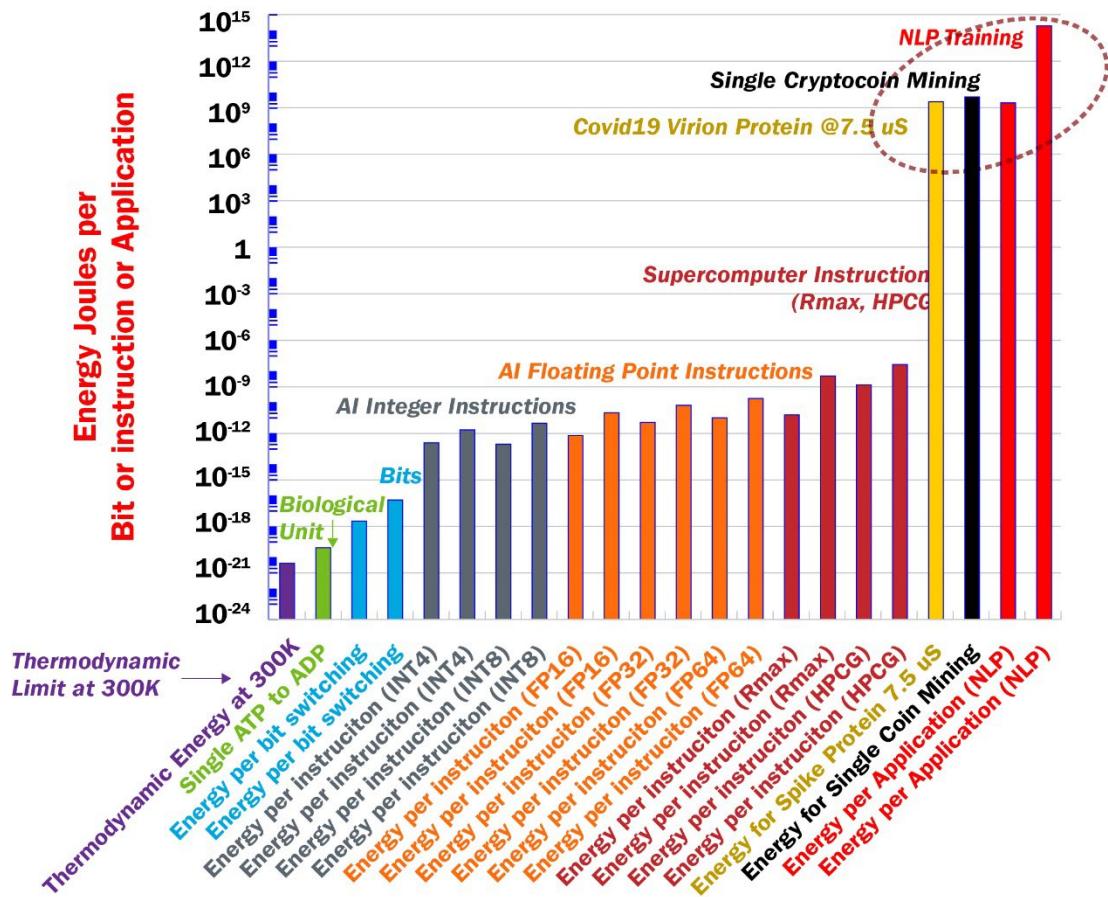

DOE’s Undersecretary for Energy and Science and the now sixty-five other external industry-based EES2 pledgers were inspired to work toward this goal and join the roadmap effort on the strength of DOE’s 2021–2022 “Semiconductor R&D for Energy Efficiency” virtual workshop series and its 2022 sponsored assessment of computing energy use (Shankar and Reuther 2022), which contributed additional insight on how the stack could be co-designed with rigorous analysis of computing performance using the metrics of energy per bit, per instruction, and per application.

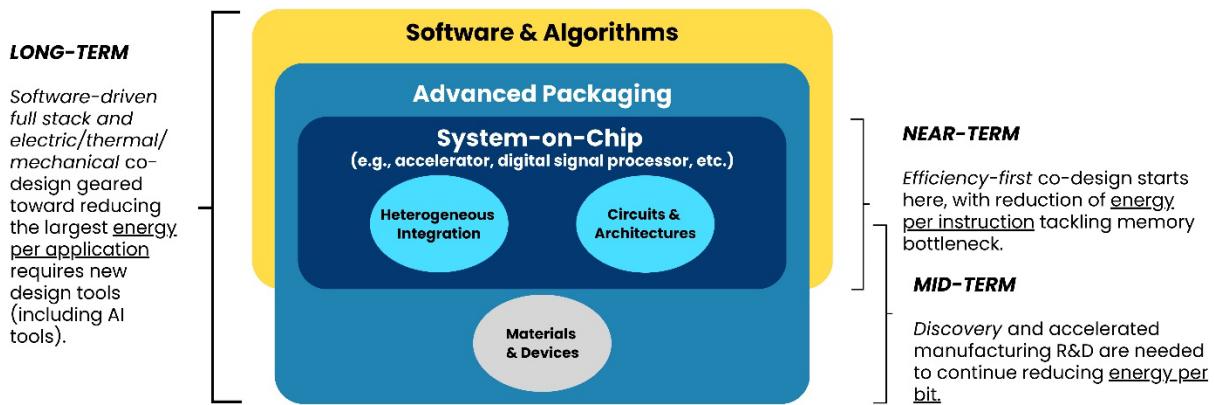

## Strategies for Efficiency First

To directly support the goals of EES2, co-design strategies are prioritized to optimize for efficiency first. Simply put, this means that where multiple properties are desired for a given technology solution, energy efficiency should be the first property for optimization in the co-design. In addition, three sub strategies emerged related to the three different energy metrics for the near-, mid-, and long-term, as shown in Figure ES-2.

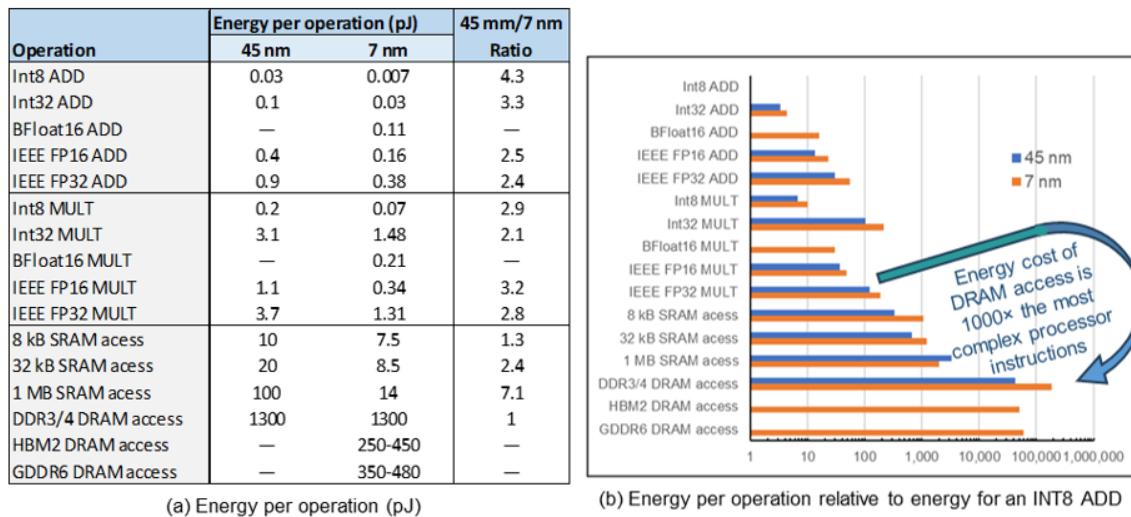

### Near-Term: Optimization of Energy per Instruction/Operation

EES2-sponsored analysis by Stanford Linear Accelerator Center (SLAC) (Shankar and Reuther 2022) showed large variation in energy per instruction or operation for different types of computational tasks. This suggests that a chip design strategy that ensures instruction complexity for a given task is as low as possible is the correct “efficiency first” hardware co-design strategy. Graphic processing units (GPUs) for gaming and artificial intelligence (AI) are a successful example of an approach of this type.

**Figure ES-1. Compute Stack.** Source: DOE Office of Science, 2018

## Mid-Term: Device-Level Innovations To Minimize Energy Use per Bit

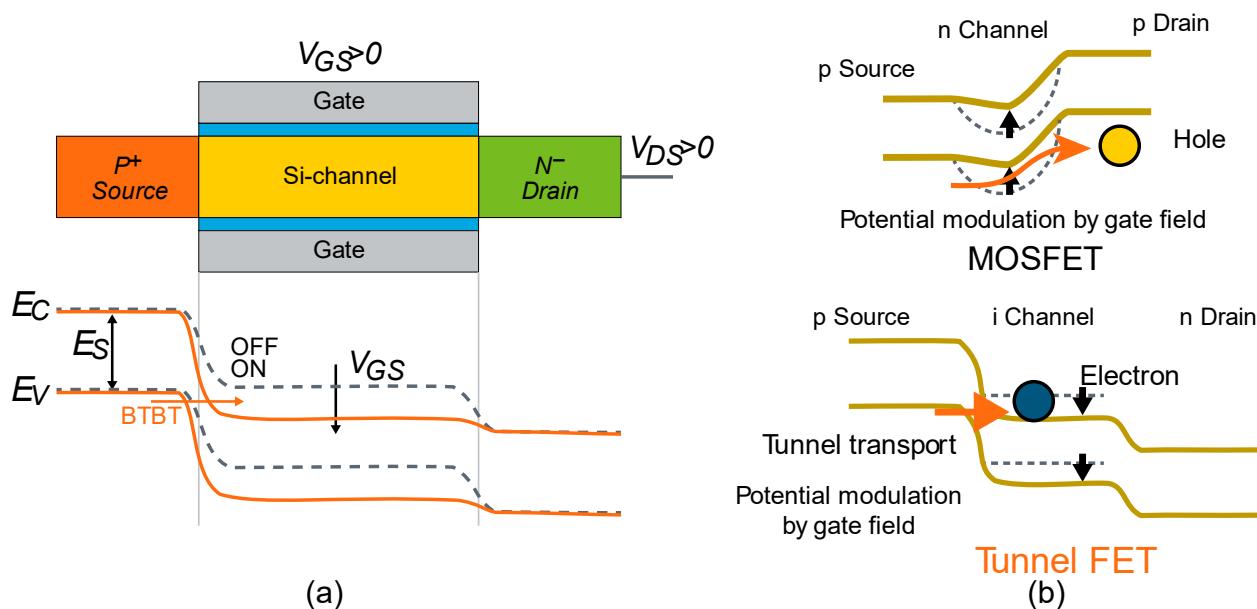

Because they are so foundational, innovations at the device level, especially with transistors, are critical. In the near- and mid-term, the EES2 roadmap highlights innovations that sharpen the subthreshold swing slope and lower switching voltage, such as tunnel field-effect transistors (TFETs). In the mid- to long-term, device level innovations from quantum and nature-inspired computing will be critical for widespread advances from 100x to 1,000x energy efficiency.

## Long-Term: Full-Stack Software-Driven Co-design To Minimize Energy per Application

The goal of full-stack co-design has yet to be implemented. This strategy is accelerating toward this goal by focusing on a subset of full-stack co-design that is software-driven, requiring that hardware developers understand what the software needs to do, and software designers understand the needs of hardware. Full implementation would require a major change in pedagogy and curriculum since software and hardware engineers have become more and more specialized in recent decades. But in the meantime, steps in this direction include specifying in algorithms that do not require high precision to save energy. Figure ES-2 illustrates the interaction between different layers of the compute stack, the timeline for the innovation, and the correlated energy metric.

Figure ES-2 Relationship of compute stack elements to achieving energy efficiency goals with different time frames

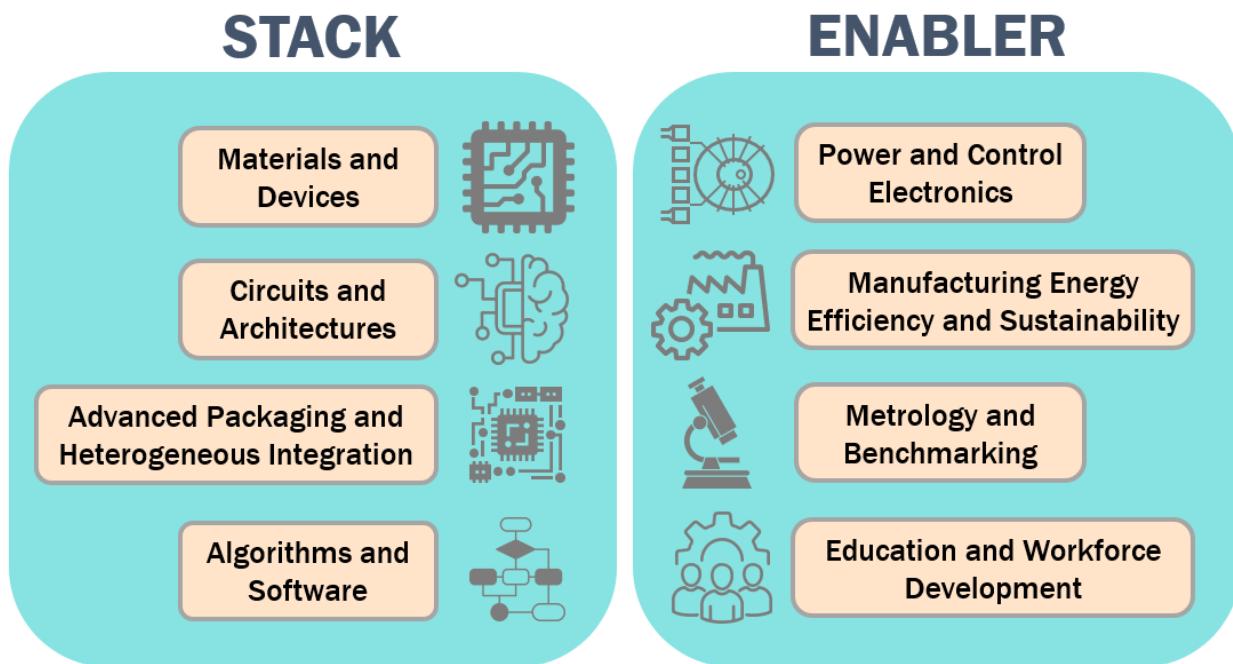

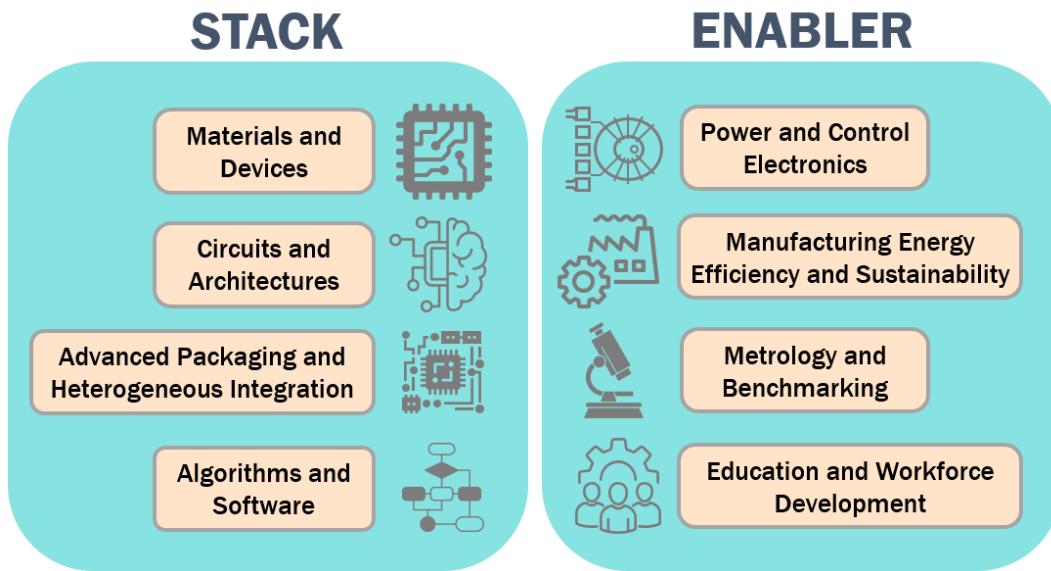

## Expanding Co-Design for the Compute Stack→ Stack Working Groups

When the concept of co-design was first applied to microelectronics, it simply meant the integration of hardware and software design in computing. Compute is the largest microelectronics system energy user—hence the focus of this roadmap. As the complexity of the compute stack grew (see Figure ES-3 left side), numerous subcategories of hardware and software were developed. In order to achieve the benefits of co-design envisioned by DOE in its seminal [Basic Research Needs for Microelectronics](#) (2018) report, co-design for energy efficiency must ensure that adjacent elements of the stack work together. AMMTO's DOE partners in SC defined co-design in this 2018 report as “where each of the technical abstraction layers in modern computer system design (the compute stack), from fundamental materials research through applications, inform and engage other abstraction layers.” Furthermore, “co-design activities largely occur between adjacent technology abstraction layers (e.g., between materials and devices or computer architects and software designers).” Therefore, the initial four

EES2 working groups (WGs) were assembled, as shown in Figure ES-3, to ensure co-design among adjacent layers.

## Pledger Experience Led to Inclusion of Enabling Layers of Co-Design

EES2 industry and laboratory pledging partners with experience in the rapidly growing data center sector also urged the inclusion of power in the WGs' co-design approach. Thus, a Power and Control Electronics WG was added. In addition, since the National Institute of Standards and Technology (NIST) had been involved with [pre-EES2 efficiency efforts](#)—and the EES2 team knew the importance of metrology to keep track of efficiency goals—a Metrology and Benchmarking WG was included from the beginning. Finally, the analysis EES2 was conducting in parallel with the WGs showed that manufacturing energy use, complexity, and chemical intensity also had begun to rise rapidly in recent years, so a Manufacturing Energy Efficiency and Sustainability WG was included.

Early in the process, the working groups realized that past efforts at co-design had not generally involved software for hardware, such as the proprietary electronic design automation (EDA) software used to design circuits. To rectify this issue, the Circuits and Architectures WG began to meet with other WGs. In 2018, the co-design was mainly between adjacent layers, but by 2023, it had become clear that every aspect of the compute stack, plus every aspect of the enablers, needed to be aligned to minimize energy use.

Figure ES-3. Organization of the EES2 working groups

With the help of cross cutting pledgers such as SRC and IEEE (the world's largest professional society), an Education and Workforce Development WG was formed. A co-design focus between working group areas is essential to make the rapid efficiency progress needed for biennial efficiency doubling and to ensure that the effort is both technically feasible and commercially viable.

The general scope of each WG is described in the following section.

## Compute Stack Co-Design Working Groups

The **Materials and Devices** group tackled energy efficiency through materials and devices, such as carbon nanotubes and spintronic memory. This included scalability, thermal management, and interface issues in current materials.

The **Circuits and Architectures** group worked to overcome the challenges of slowing planar geometric scaling of transistors and memory. This group pioneered alternative, energy-efficient designs in processors and memory systems, including compute-in-memory technologies.

The **Advanced Packaging and Heterogeneous Integration** group at the next level up in the compute stack, worked on advanced thermal management techniques, and optimizing data movement strategies such as optical interconnects.

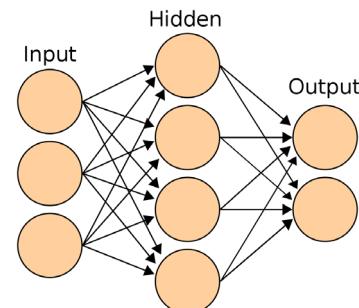

The **Algorithms and Software** group emphasized software-driven co-design and were inspired by natural systems such as dragonflies and human brains to benchmark neuromorphic algorithms matched directly with accelerator hardware.

**Table ES-1. Condensed Focus Areas for Energy Efficiency and their Manufacturing Challenges & Solutions<sup>a</sup>**

| Focus Areas for Energy Efficiency                                                                                              | Manufacturing Challenges & Solutions                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Materials and Devices (Mid-Term)</b>                                                                                        |                                                                                                                                                                                                                                     |

| Innovate in materials such as 2D materials, carbon nanotubes (CNTs), and ferroelectric materials for future CMOS alternatives. | Address production and integration challenges by investing in scalable high-quality material manufacturing and creating industry-wide standards and protocols.                                                                      |

| <b>Circuits and Architectures (Near-Term)</b>                                                                                  |                                                                                                                                                                                                                                     |

| Enhance energy efficiency in compute architectures and memory technologies.                                                    | Prioritize advanced electronic design automation (EDA) and new architectures integrated with algorithms to optimize power distribution and increase energy efficiency, backed by continued investment in novel device technologies. |

| <b>Advanced Packaging and Heterogenous Integration (Near-Term)</b>                                                             |                                                                                                                                                                                                                                     |

| Develop vertically integrated, energy-efficient 3D technology stacking.                                                        | Pair novel technologies with state-of-the-art processors/memories to show durability and enhance intra-chip energy efficiency, improving EDA for system-level cooling and interconnect scaling.                                     |

| <b>Algorithms and Software (All Time Scales but Especially Long-Term)</b>                                                      |                                                                                                                                                                                                                                     |

|                                                                                                                |                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Innovate in machine learning algorithms and software that efficiently support diverse computing architectures. | Develop machine learning optimization through meta-learning and exploit massively parallel computing systems more effectively, using advanced parallelization of code. |

|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

<sup>a</sup> For complete list, refer to Table 85.

## Crosscutting Co-Design Working Groups (Also Known as Enablers)

The **Power and Control Electronics** group focused on enhancement and innovation of power delivery systems on chip as well as in energy intensive applications such as data centers.

The **Manufacturing Energy Efficiency and Sustainability** group looked at the correlation between less efficient products and less efficient manufacturing processes to make them. The group also explored other energy-related environmental impacts of manufacturing.

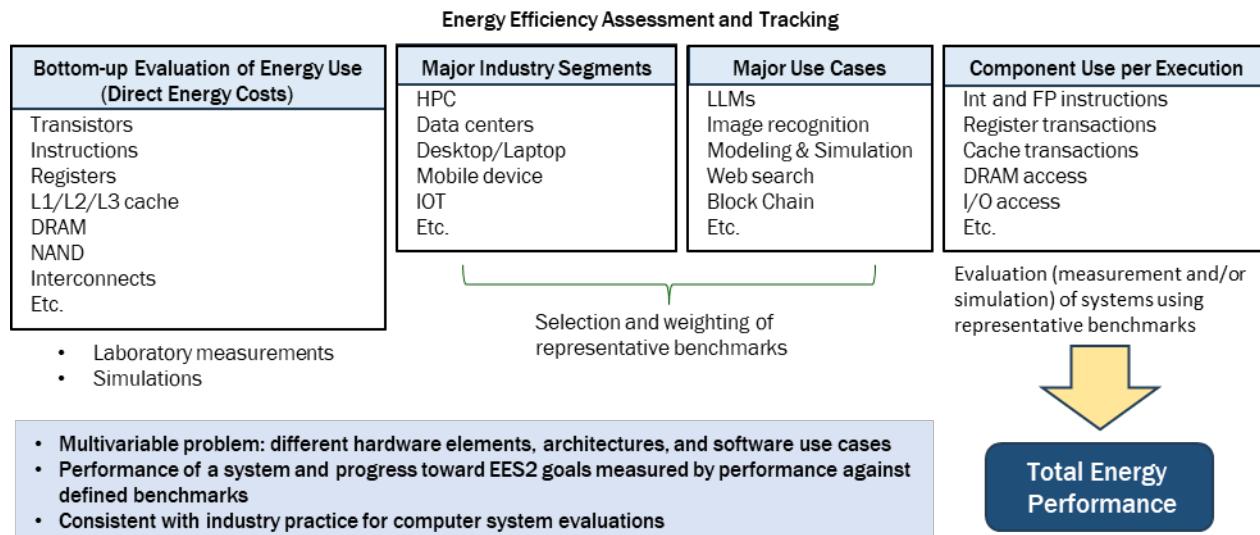

The **Metrology and Benchmarking** group defined measurement and benchmarking standards necessary to evaluate emerging microelectronic technologies.

The **Education and Workforce Development** group took advantage of the compelling EES2 benefits to the planet for efforts to convince policy makers and potential new industry employees.

**Table ES-2. Condensed Focus Areas for Energy Efficiency and Their Grand Challenges and Solutions<sup>a</sup>**

| Focus Areas for Energy Efficiency                                                                                                                             | Manufacturing Challenges and Solutions                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Power and Control Electronics (Very Near-Term)</b>                                                                                                         |                                                                                                                                                                                                    |

| Enhance power delivery and control across microelectronics to data centers by migrating loads to higher-efficiency regions and utilizing renewable resources. | Develop resource-aware scheduling strategies and implement advanced co-design tools to optimize power provisioning and thermal management, reducing overall energy consumption.                    |

| <b>Manufacturing Efficiency and Environmental Sustainability (Near-Term)</b>                                                                                  |                                                                                                                                                                                                    |

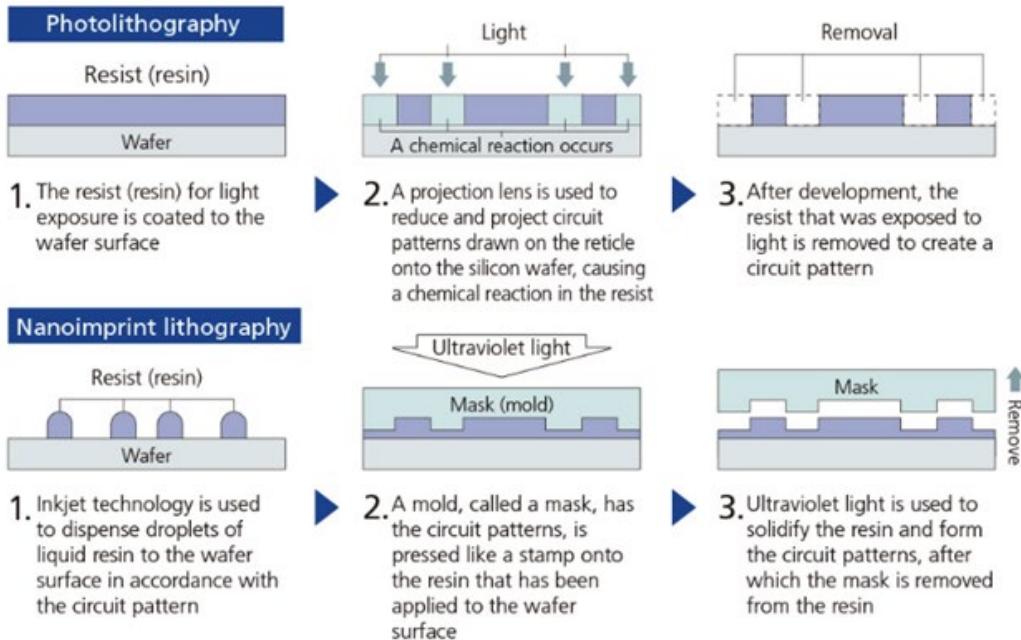

| Improve manufacturing processes to lower greenhouse gas emissions and energy consumption.                                                                     | Introduce alternative gases and processes with lower environmental impacts and invest in alternate lithography technologies like nanoimprint lithography (NIL) for energy-efficient manufacturing. |

| <b>Metrology and Benchmarking (All Time Scales)</b>                                                                                                           |                                                                                                                                                                                                    |

| Advance metrology by integrating AI/ML in nondestructive, high-resolution techniques to evaluate complex structures and materials accurately.                 | Establish comprehensive benchmarking standards and develop advanced metrology tools for real-time analysis, bridging the gap between traditional methods and the needs of emerging technologies.   |

| <b>Education and Workforce Development (All Time Scales but Especially Long-Term)</b>                                                                         |                                                                                                                                                                                                    |

|                                                                                                               |                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cultivate a skilled workforce attuned to the demands of energy-efficient microelectronics and sustainability. | Align educational outcomes with industry needs, implement targeted training programs, and promote inclusivity to build a diverse workforce capable of driving global innovation. |

|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

<sup>a</sup> For complete list, refer to Table 86.

## Key Technologies Identified

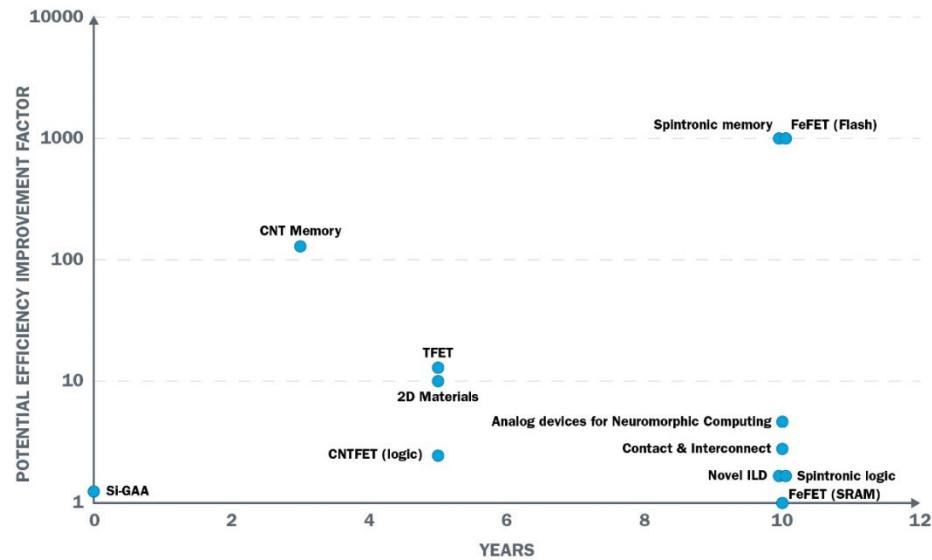

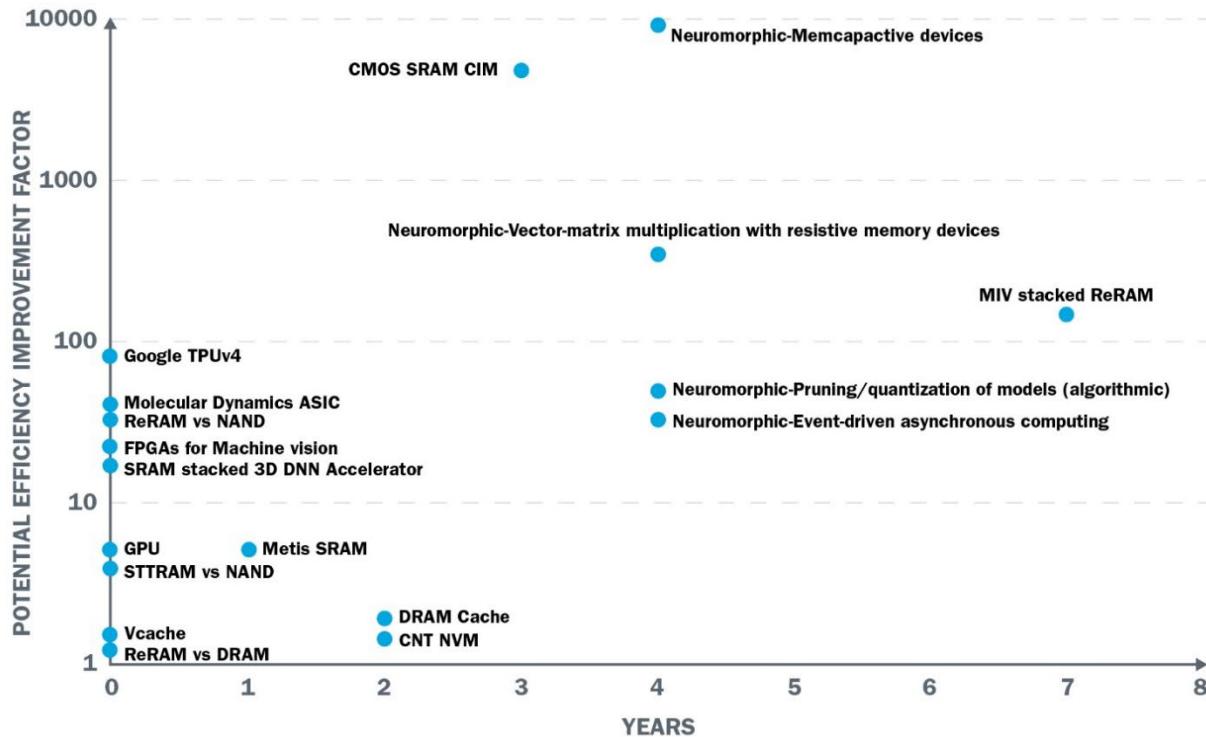

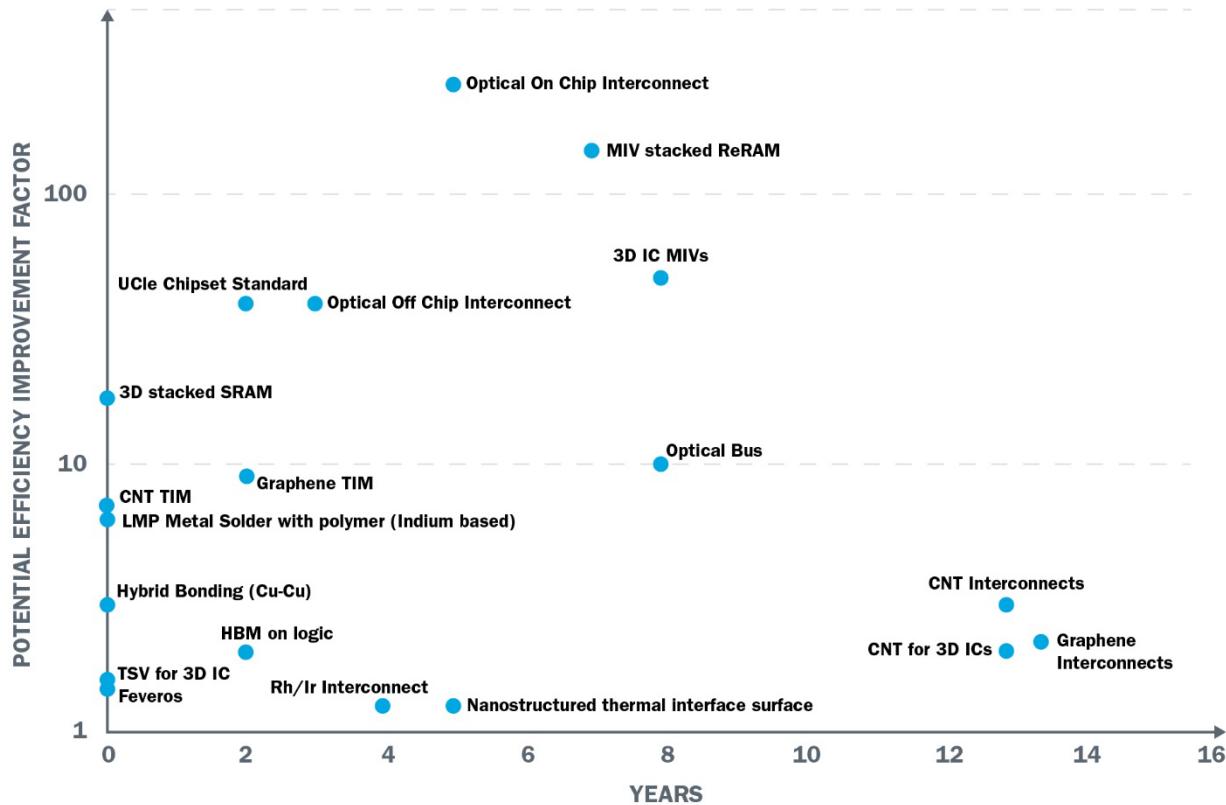

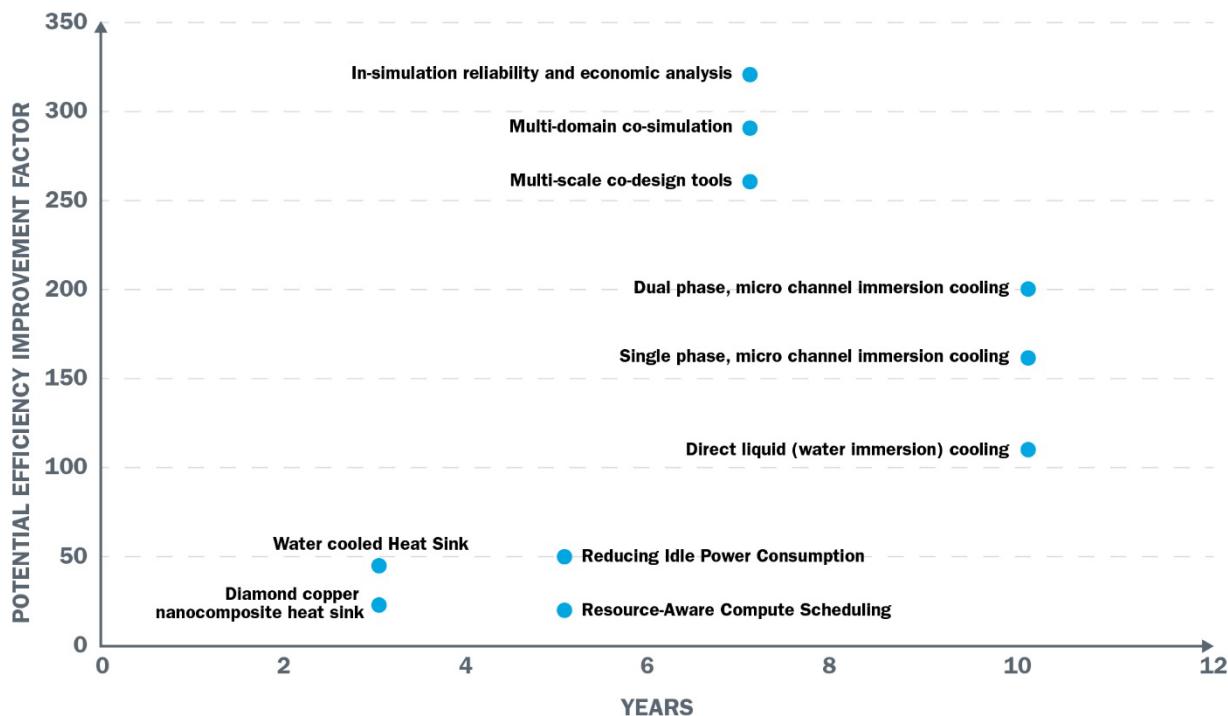

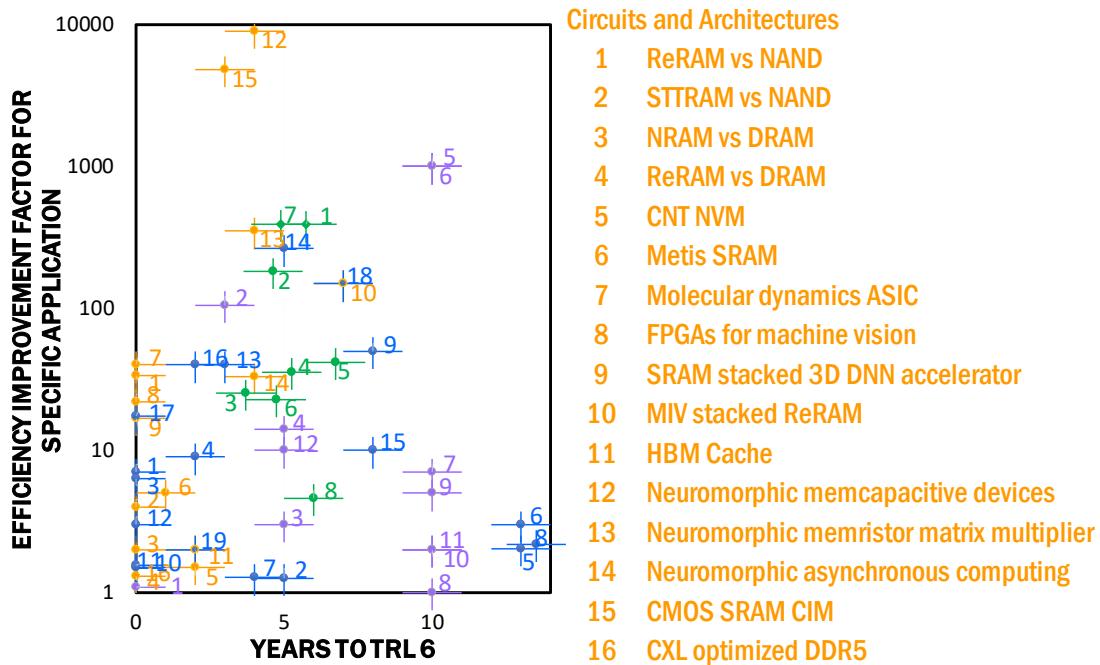

Figure ES-4 graphically illustrates some promising technology options identified in this roadmap by adjacent co-design approaches to the compute stack, sorted by working group.

Figure ES-4. Key energy-efficient technologies for industry researchers to beat in each epoch

The figure illustrates one of two major criteria used by the working groups in evaluating candidate EES2 technologies: factor of efficiency improvement based on energy metrics (e.g., energy per bit, energy per switch, memory access) compared to state-of-the-art technologies. Note the semi-log tick marks where the efficiency factor increases logarithmically to the right.

Note that these technologies do not in any way represent a government plan for energy efficiency. Rather these technologies and the technology areas from which they spring are technologies with “energy efficiency to beat.” Rather than being a plan or even a forecast, the roadmap seeks to provide benchmarks that will inspire technology developers to apply the recommended efficiency first design principles and possibly prove wrong dire predictions for future computing energy use.

## Next Steps

This version 1.0 of the EES2 roadmap is the end of the beginning of a two-decade effort to take energy efficiency scaling from historical fact to future reality. The demand for computing and the critical need to curb emissions require an acceleration and expansion of current initiatives.

In addition to the roadmap, DOE intends for the EES2 partners to begin a cycle of challenging one another on increasingly ambitious energy efficiency goals. For example, AMD has already begun to challenge the industry on AI chip efficiency—and a response from other AI chip makers is hopefully forthcoming soon. Other non-roadmap EES2 activities planned for the pledgers include the establishment of a testing facility to measure the relative efficiency of highly energy-intensive software (e.g., AI training, Transformer) due to the emergence of many different AI chip architectures. Such a testing facility would also verify the orders of magnitude efficiency improvements of AMMTO and other government funded hardware, such as TFET and neuromorphic chips.

Finally, AMMTO hopes that the EES2 partners will continue to document and learn from microelectronics' past and forecasted future ability to enable all sectors of the economy to become more energy efficient and sustainable. EES2 partners will also continue to identify and publicize the problems solved and the opportunities offered by the roadmap 1.0 and the analysis performed for EES2. A surge in energy use forecasted for data centers is the first of many challenges to which the EES2 community will forcefully respond. Future potential energy-use surges related to communications (such as those that may accompany 6G+) will also be identified, documented, learned from, and publicized by the EES2 community as it evolves from a government-led organization to one that is privately led.

While this report documents myriad potential efficiency improvements across 55 technologies, achieving their full benefits requires an integrated approach that emphasizes software-driven co-design across the entire technology stack. Ultimately, EES2 hopes to reboot the energy efficiency doubling pace of Dennard scaling doubling efficiency every two years—with the goal of reaching 1,000 times more in the next 20 years.

Plans for roadmap 2.0 are already underway. As DOE and its partners recruit more industrial, academic, and national laboratory members for the EES2 innovation ecosystem, the initiative will not only have more policy impact, but it will also boast even broader technical expertise among the WGs. Now that the first roadmap is published, EES2 will actively turn to broaden its recruiting into new microelectronics application sectors, such as communications. In addition, while EES2 started with electronics and electrons, it will also broaden to promising new information carriers, such as the photons used in optoelectronics and photonics. EES2 already includes pledgers whose research includes long-term transformational technology areas such as quantum computing as well as the latest advances in nature-inspired architectures. EES2 will work with these pledgers to help recruit additional pledgers from their respective sectors and to attract more volunteers for the version 2.0 WGs.

Although much can change before the start of version 2.0 of the roadmap in spring 2025, future WGs will continue to build upon a solid base of peer-reviewed research while continuing to work with EES2 pledgers to lower barriers toward immediate deployment of technologies for biennial microelectronics energy efficiency doubling. This dual R&D and deployment strategy ensures flexibility and responsiveness to emerging technologies and market shifts, thereby fostering a sustainable evolution of the microelectronics sector.

As the EES2 Initiative continues to grow and build momentum for massive improvements in computing energy efficiency, the EES2 team will work further with stakeholders in microelectronics and related applications to develop the technology base and to assess progress toward the goal every 2 years.

This roadmap is not intended to serve as a forecast or to pick winners and losers among technologies. Rather, it is the opening salvo in a new energy efficiency “space race,” where instead of outer space, the EES2 team explores the fascinating realm of increasingly tiny and ultra energy efficient information systems. The roadmap sets a high bar to challenge and motivate technology developers and to counteract grim forecasts that humanity cannot achieve the clean energy transition due to rising computing energy use trends. The semiconductor industry’s inspiring past successes in improving energy efficiency indicate that ambitious EES2 efficiency goals can be met as well. Let’s do it now.

## Table of Contents

|                                                                     |     |

|---------------------------------------------------------------------|-----|

| Executive Summary .....                                             | xiv |

| 1 Introduction .....                                                | 1   |

| 1.1 Background .....                                                | 1   |

| 1.2 Scope of the Problem .....                                      | 7   |

| 1.3 Key Concepts for Microelectronic Energy Efficiency .....        | 12  |

| 1.4 Organization of the Work .....                                  | 13  |

| 1.5 Methodology .....                                               | 16  |

| 1.6 Related Work .....                                              | 18  |

| 1.7 Introduction References .....                                   | 21  |

| 2 Technologies for the Compute Stack .....                          | 24  |

| 2.1 Materials and Devices .....                                     | 24  |

| 2.2 Circuits and Architectures .....                                | 89  |

| 2.3 Advanced Packaging and Heterogeneous Integration .....          | 130 |

| 2.4 Algorithms and Software .....                                   | 173 |

| 3 Enablers .....                                                    | 226 |

| 3.1 Power and Control Electronics (PACE) .....                      | 226 |

| 3.2 Manufacturing Energy Efficiency and Sustainability (MEES) ..... | 251 |

| 3.3 Metrology and Benchmarking .....                                | 264 |

| 3.4 Education and Workforce Development (EWD) .....                 | 281 |

| 4 Conclusion .....                                                  | 298 |

| 4.1 A New Moonshot and Space Race .....                             | 298 |

| 4.2 EES2: Putting People and Their Organizations First .....        | 300 |

| 4.3 Technology Results and Co-Design for Efficiency First .....     | 300 |

| 4.4 The Future .....                                                | 305 |

| 5 Bibliography .....                                                | 306 |

## List of Figures

|                                                                                                                          |      |

|--------------------------------------------------------------------------------------------------------------------------|------|

| Figure ES 1. SRC energy consumption forecast and the EES2 efficiency goal in two energy consumption scenarios .....      | xiv  |

| Figure ES-1. Compute Stack .....                                                                                         | xv   |

| Figure ES-2 Relationship of compute stack elements to achieving energy efficiency goals with different time frames ..... | xvi  |

| Figure ES-3. Organization of the EES2 working groups .....                                                               | xvii |

| Figure ES-4. Key energy-efficient technologies for industry researchers to beat in each epoch                            | xx   |

|                                                                                                                                                            |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1. The 2023 version of the SRC computing energy use forecast .....                                                                                  | 3  |

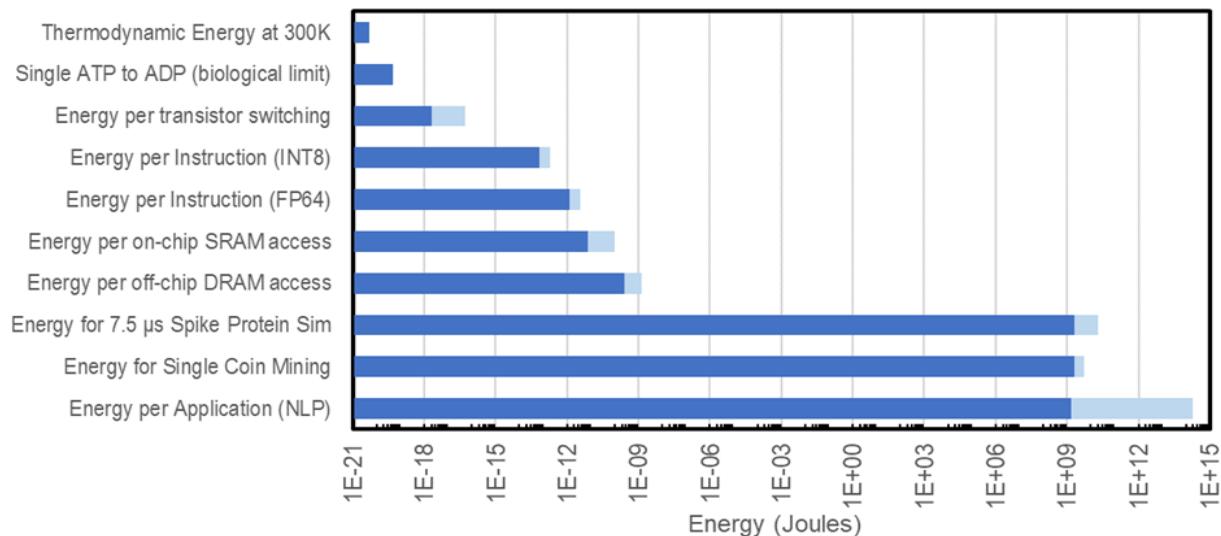

| Figure 2. Analysis of the opportunity space for energy efficiency (from bits to bitcoin) according to the bits, instructions and application metrics. .... | 6  |

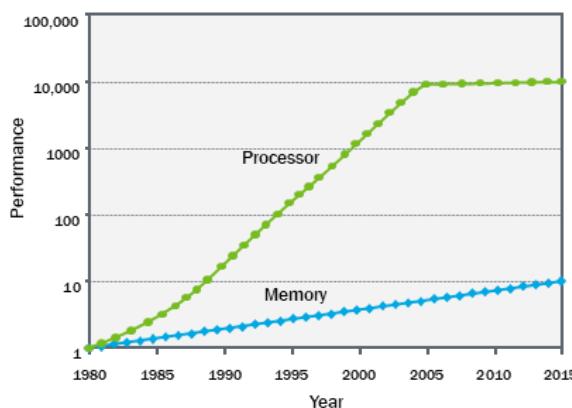

| Figure 3. 50 years of microprocessor trend data. ....                                                                                                      | 7  |

| Figure 4. The gap between processor performance and DRAM latency. ....                                                                                     | 8  |

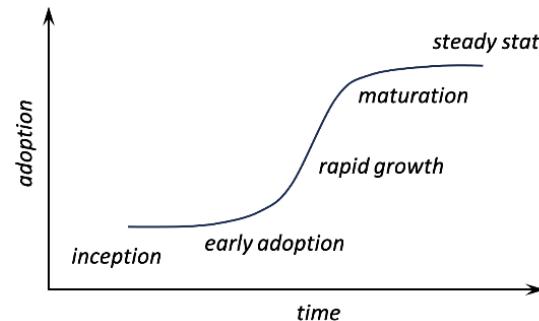

| Figure 5. S-curve model.....                                                                                                                               | 8  |

| Figure 6. Scale of energy use from bits to applications .....                                                                                              | 10 |

| Figure 7. Energy cost for various operations .....                                                                                                         | 11 |

| Figure 8. The compute stack. ....                                                                                                                          | 13 |

| Figure 9. 2022–2023 organization of the EES2 working groups. ....                                                                                          | 14 |

| Figure 10. Definitions for technology readiness levels for the microelectronics industry as used in this report .....                                      | 18 |

| Figure 11. Technology options for new information processing technologies. ....                                                                            | 24 |

| Figure 12. Potential efficiency improvement factor and timeline for selected technologies proposed by the Materials and Devices working group .....        | 25 |

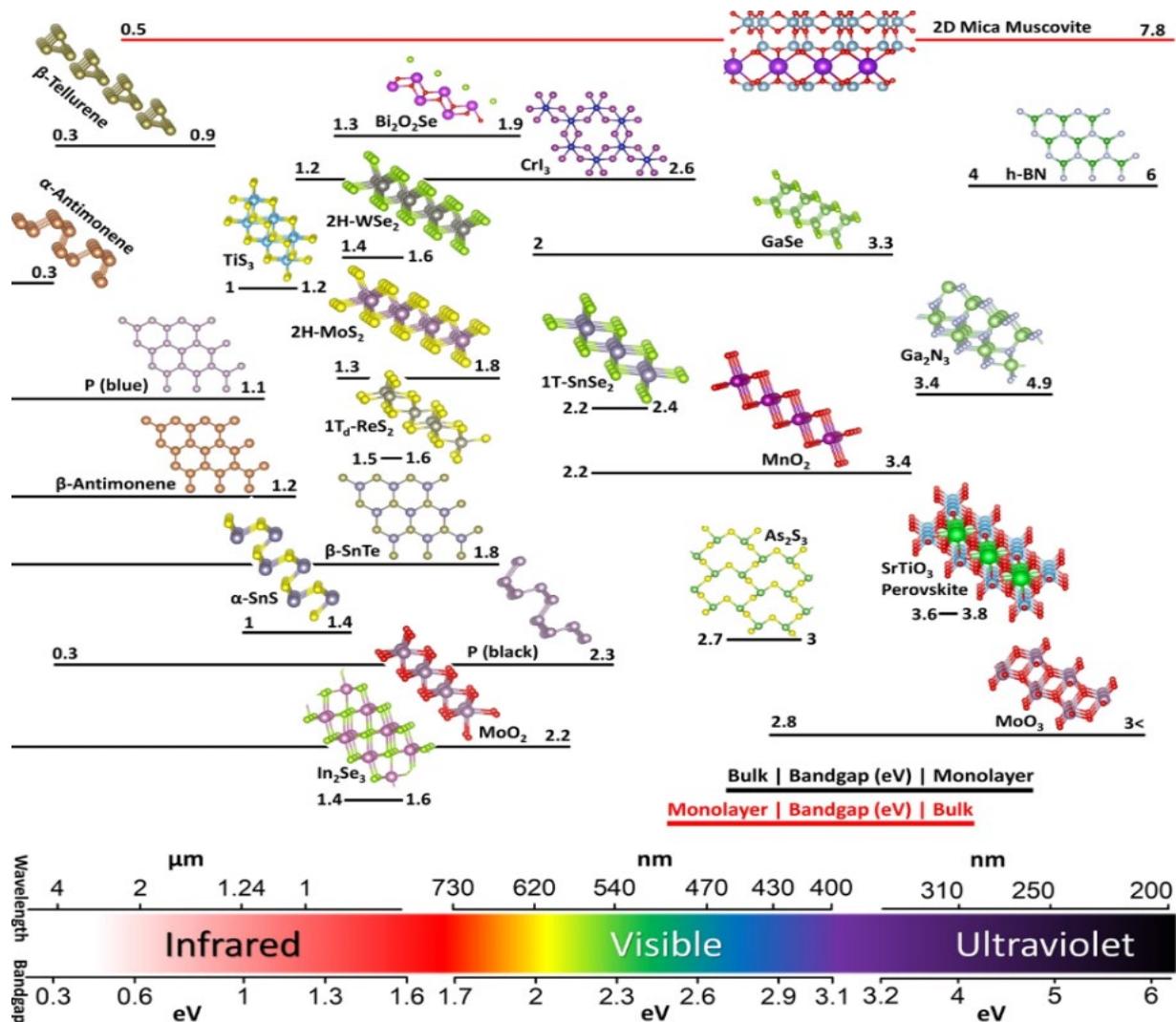

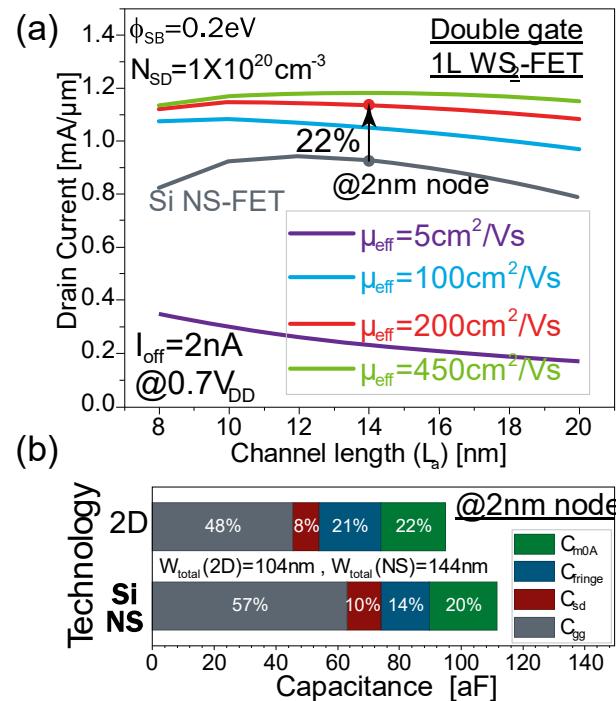

| Figure 13. Selected 2D materials and their bandgap.....                                                                                                    | 28 |

| Figure 14. Si NS-FET versus 2D-FET. ....                                                                                                                   | 29 |

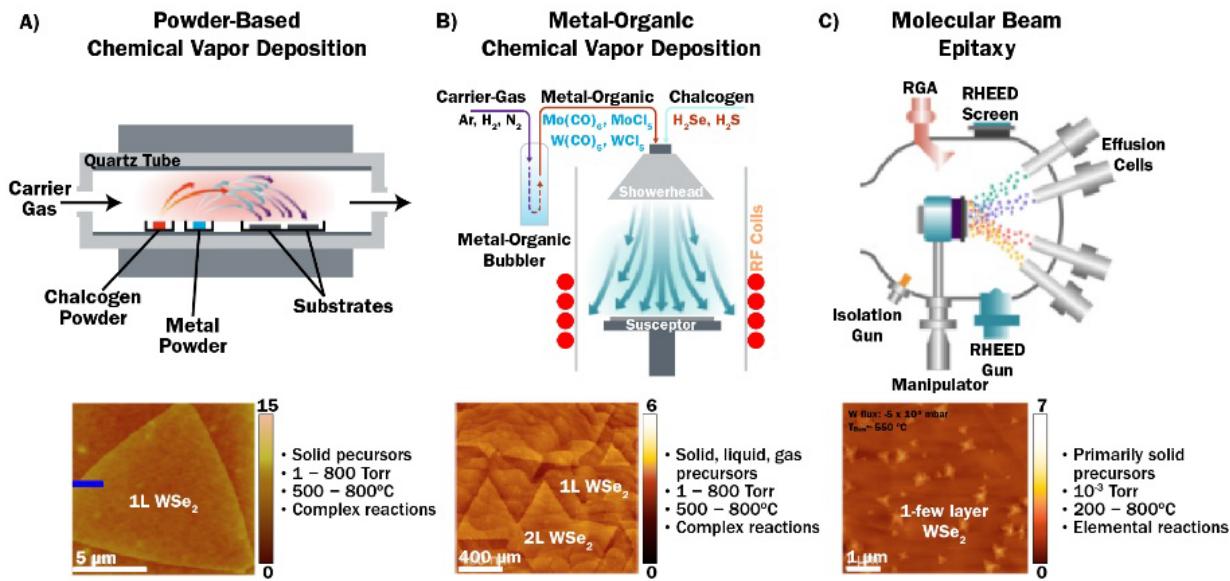

| Figure 15. Overview of synthesis techniques of single to few layer TMDC flakes. ....                                                                       | 31 |

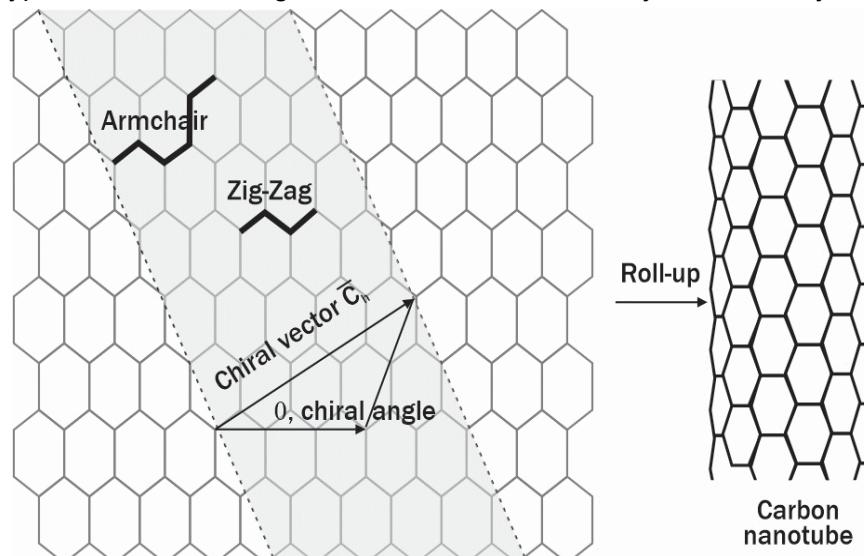

| Figure 16. Graphene lattice with chiral angle and vector for CNT, along with two dominant CNT configurations (armchair and zigzag). ....                   | 33 |

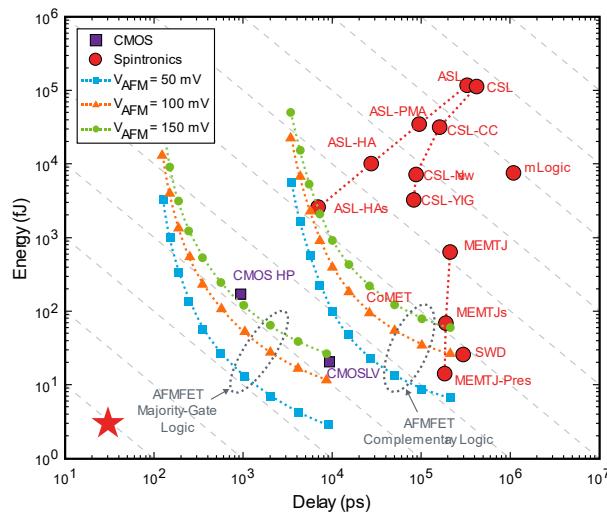

| Figure 17. Comparison of energy and delay of a 32-bit adder among various charge- and spin-based devices. ....                                             | 41 |

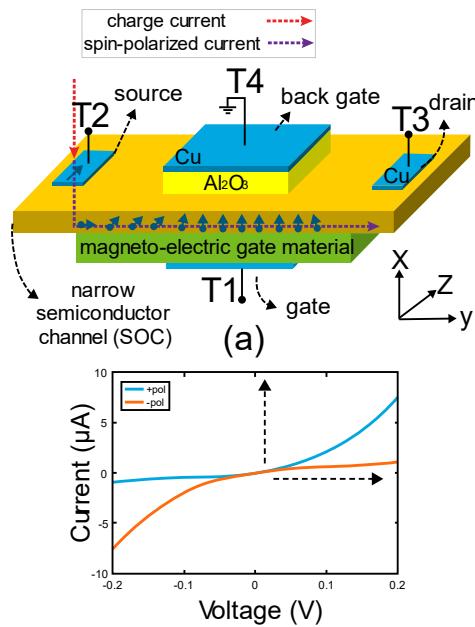

| Figure 18. The magnetoelectric FET with performance shown for a channel with a spin-orbit splitting of only 100 meV.....                                   | 41 |

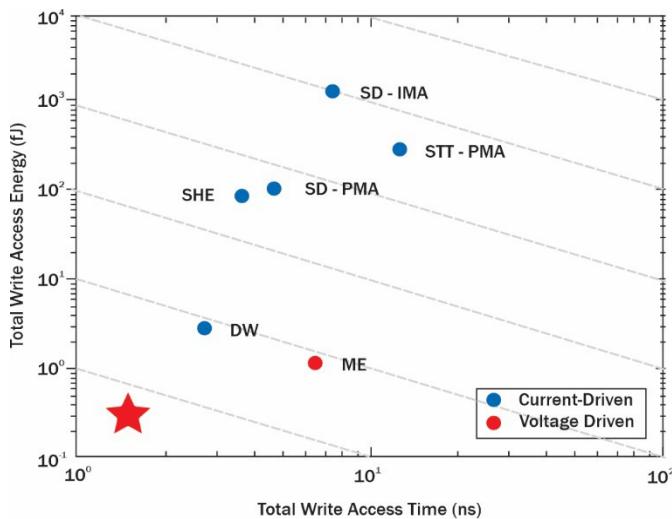

| Figure 19. Write energy vs. write delay for various types of spintronic memory cells. ....                                                                 | 45 |

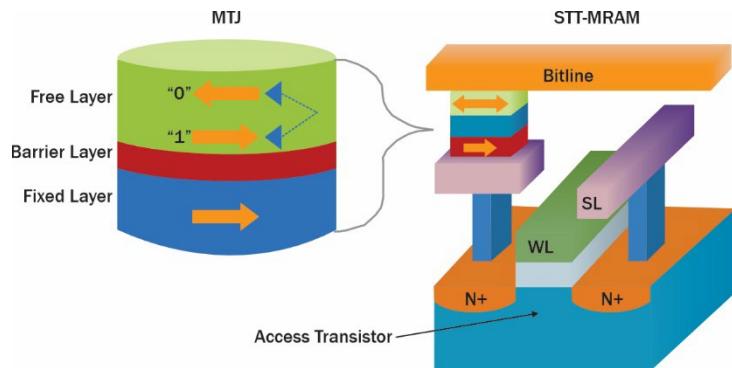

| Figure 20. STT-MRAM device structure. ....                                                                                                                 | 46 |

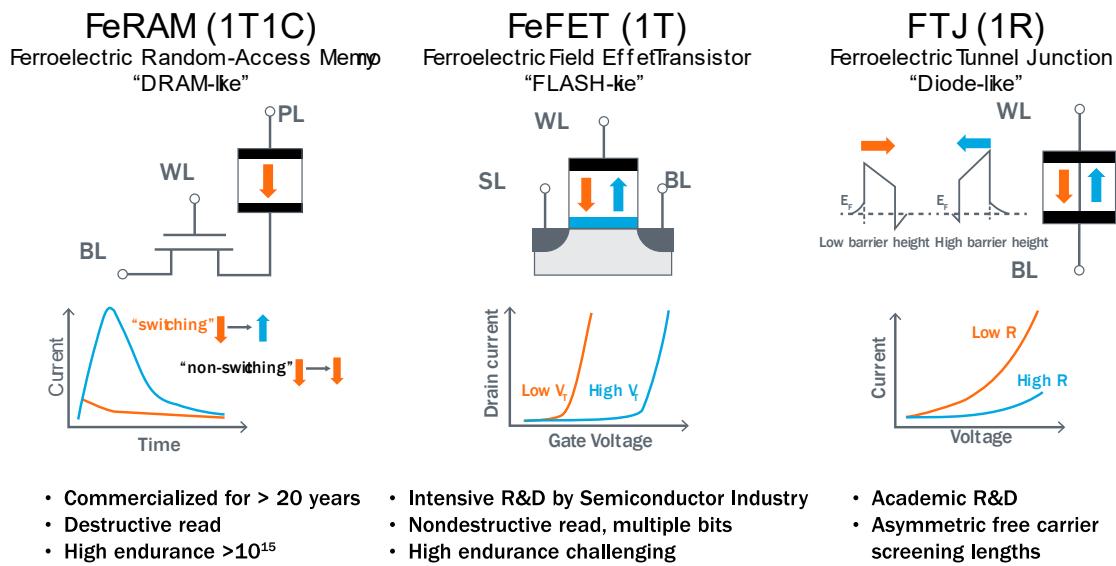

| Figure 21. Operating principles of ferroelectric memory. ....                                                                                              | 49 |

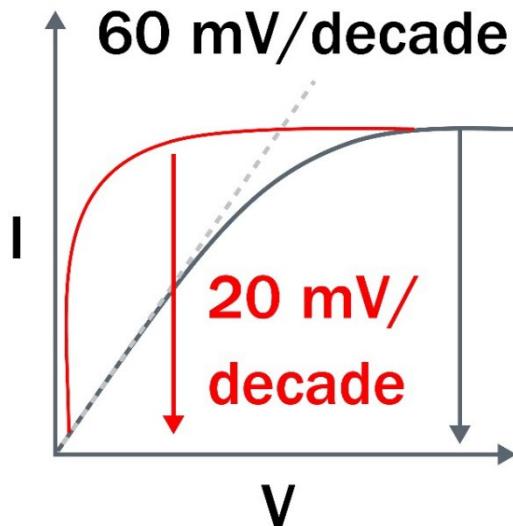

| Figure 22. Subthreshold Slope of I/V on/off curve for typical FET and subthreshold sharpening tech (e.g. TFET). ....                                       | 54 |

| Figure 23. Device operation of a tunnel field-effect transistor (TFET). ....                                                                               | 55 |

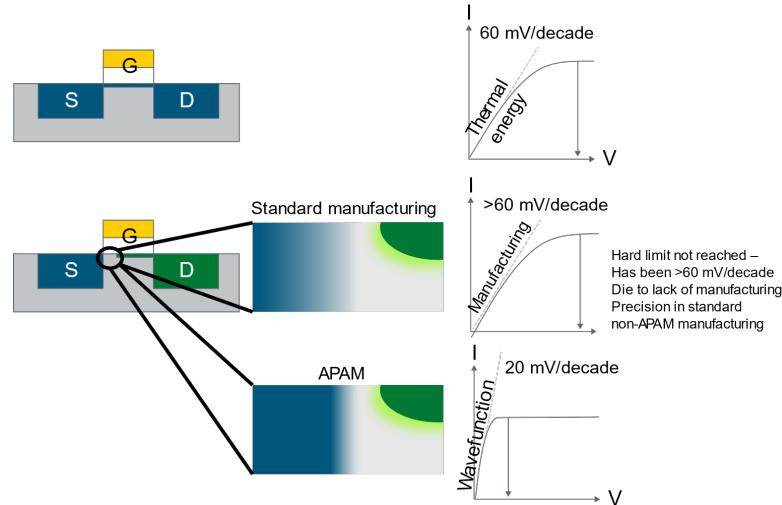

| Figure 24. Enhanced ON current and subthreshold slope with atomically precise advanced manufacturing (APAM). ....                                          | 57 |

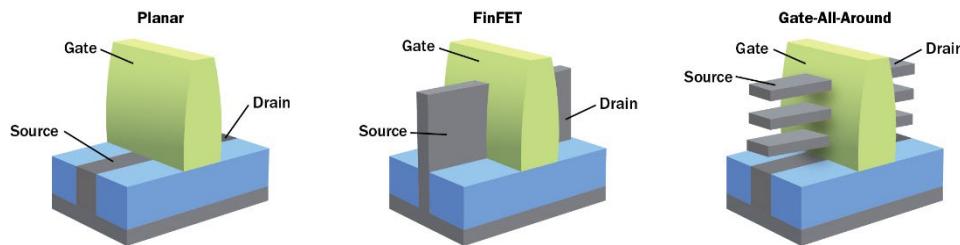

| Figure 25. Typical source, drain, and gate arrangements for planar, FinFET, and GAA transistors. ....                                                      | 60 |

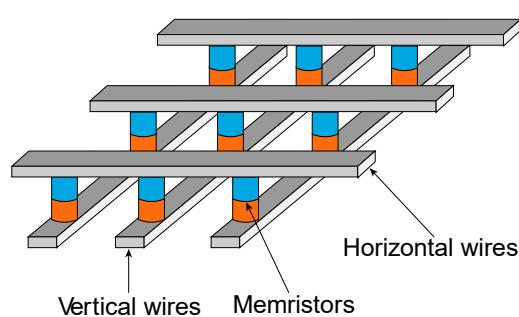

| Figure 26. Basic schematic of memristors in crossbar arrays. ....                                                                                          | 64 |

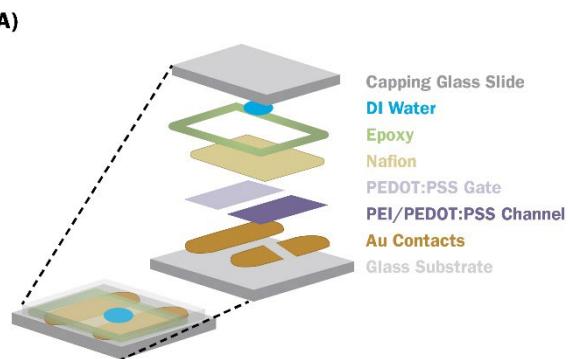

| Figure 27. Novel encapsulation strategy. ....                                                                                                              | 65 |

| Figure 28. Schematic of pore stuffing method. ....                                                                                                         | 69 |

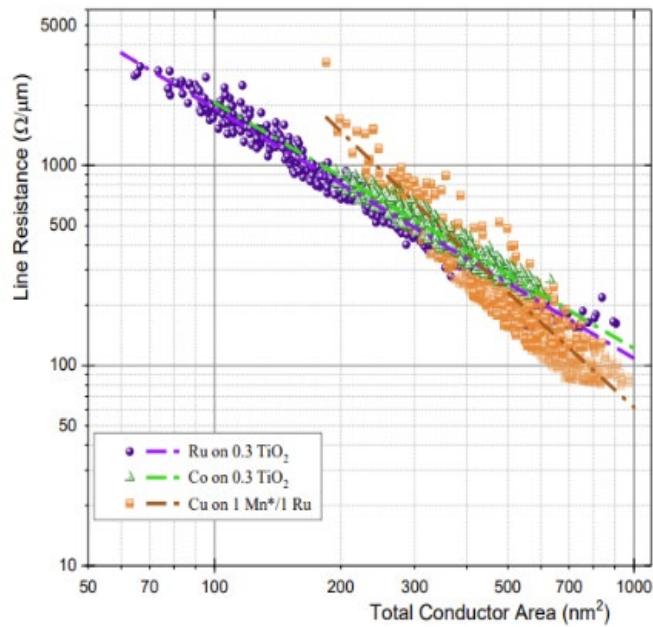

| Figure 29. Logarithmic comparison of the damascene line resistance vs. the total conductor cross-sectional area of Ru, Co, and Cu nanowires.....           | 71 |

| Figure 30. Potential efficiency improvement factor and timeline for selected technologies of the Circuits and Architectures working group. ....            | 91 |

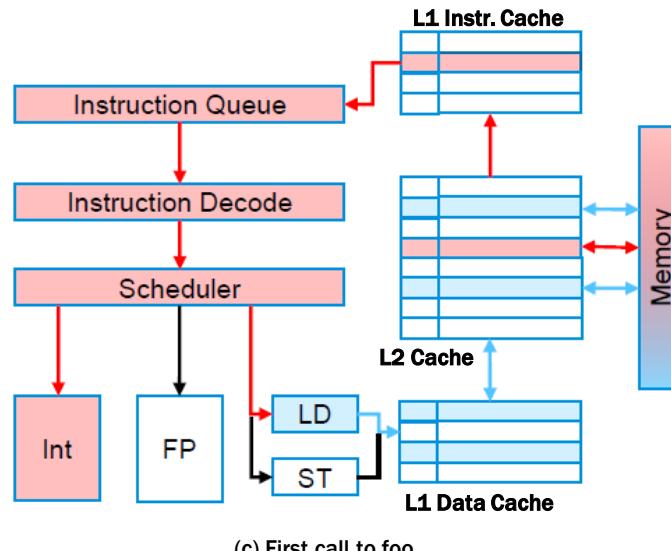

| Figure 31. Classical von Neumann computer architecture. ....                                                                                               | 93 |

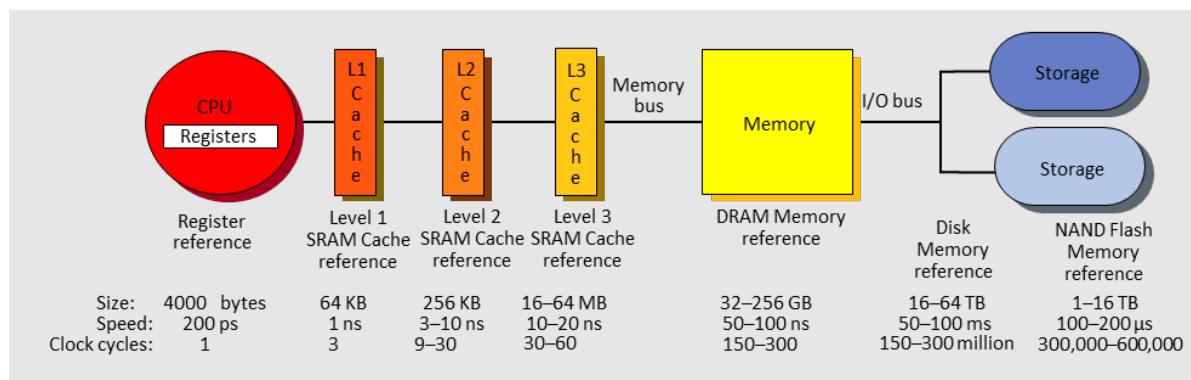

| Figure 32. Typical memory hierarchy sizes and access times (c. 2019).....                                                                                  | 93 |

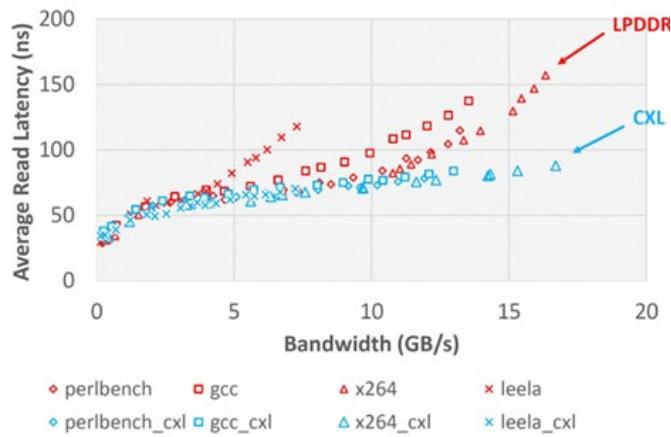

|                                                                                                                                             |     |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 33. CXL Native DRAM 8-lane PCIe Gen5 vs. LPDDR 2x LPDDR-6400 latency vs. bandwidth comparison.....                                   | 95  |

| Figure 34. Potential efficiency improvement factor and timeline for selected technologies of the APHI working group.....                    | 132 |

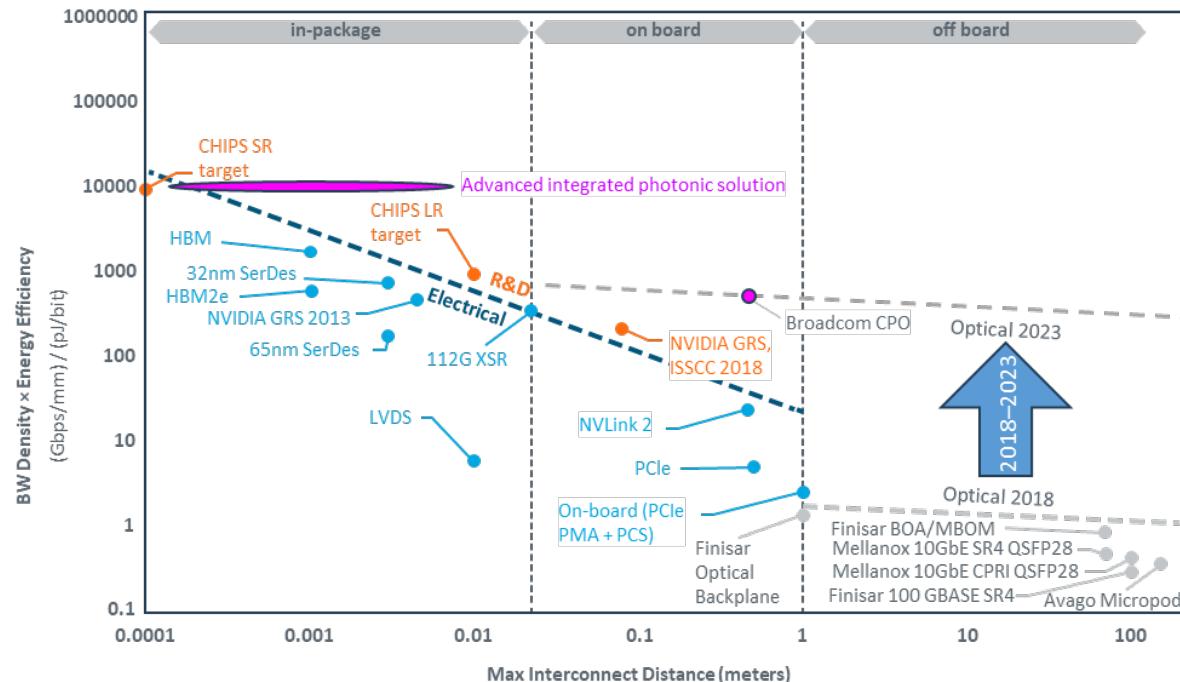

| Figure 35. Interconnect figure of merit benchmarks (circa 2018) with 2023 commercial and R&D optical interconnect benchmark references..... | 138 |

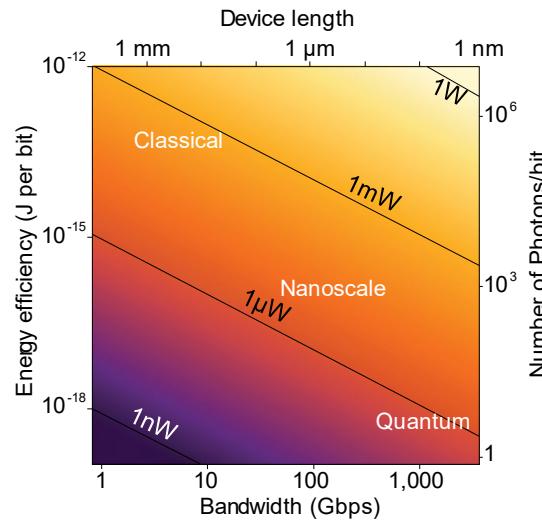

| Figure 36. Optoelectronic modulator device scaling laws.....                                                                                | 140 |

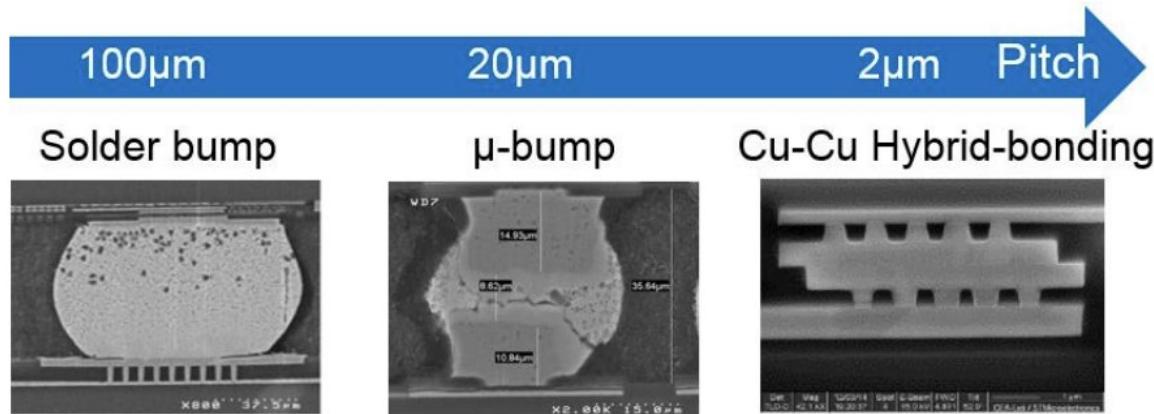

| Figure 37. Comparative images and size scales for solder, microbump, and 3D hybrid bonding interconnects. Source: Jani 2019.....            | 144 |

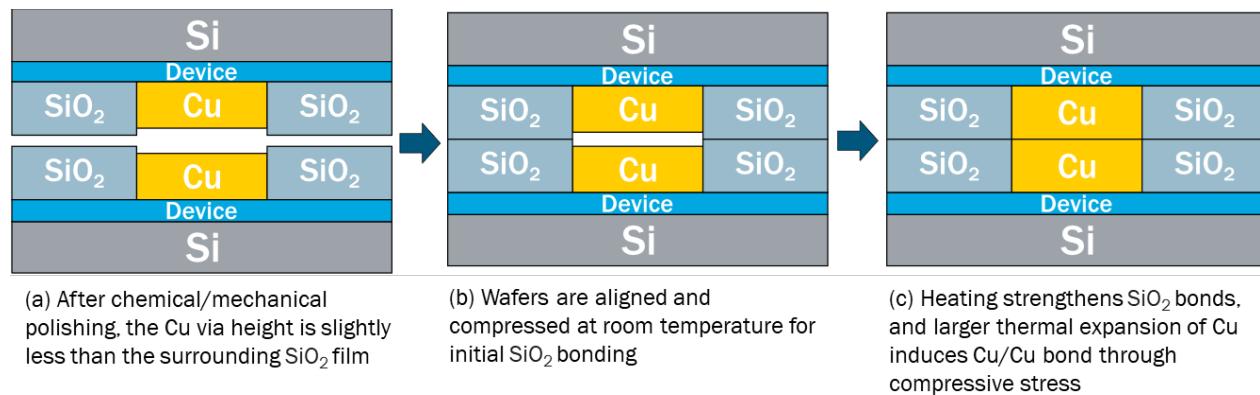

| Figure 38. 3D hybrid bonding process with Cu vias and SiO <sub>2</sub> films.....                                                           | 145 |

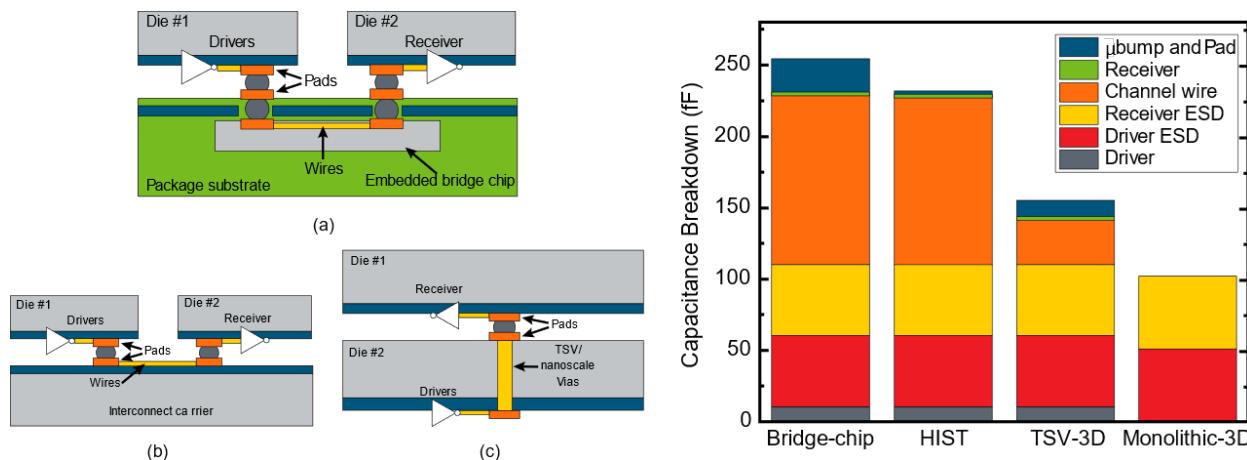

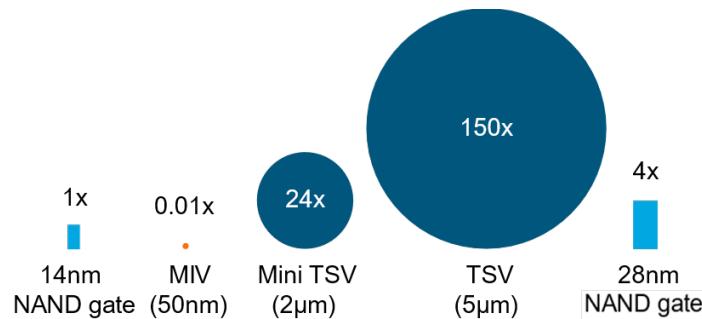

| Figure 39. Digital signal channel paths and associated capacitance.....                                                                     | 149 |

| Figure 40. Relative sizes of typical NAND gates, MIVs, and TSVs. Source: Samal et al. 2016151                                               |     |

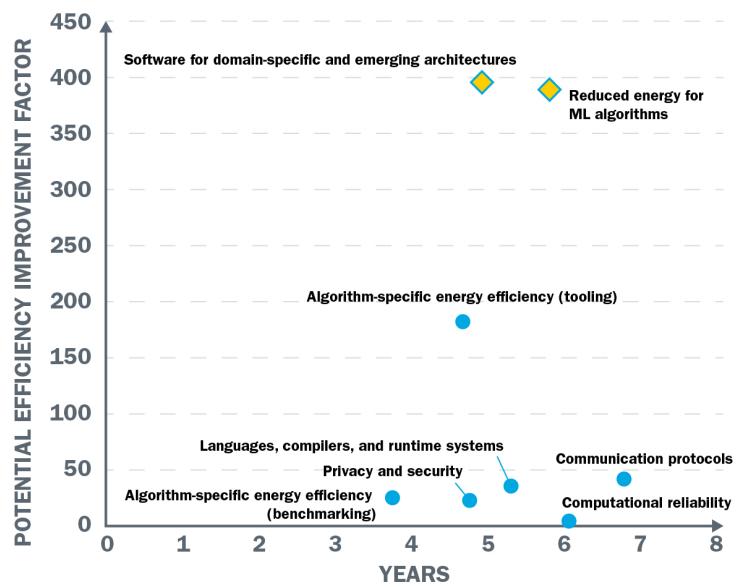

| Figure 41. Algorithms and Software working group potential efficiency improvement factor and timeline initial assessment.....               | 173 |

| Figure 42. Interaction of software and CPU architecture.....                                                                                | 177 |

| Figure 43. EES2 proposed approach to evaluation of computer system energy performance and progress toward long-term improvement goals.....  | 181 |

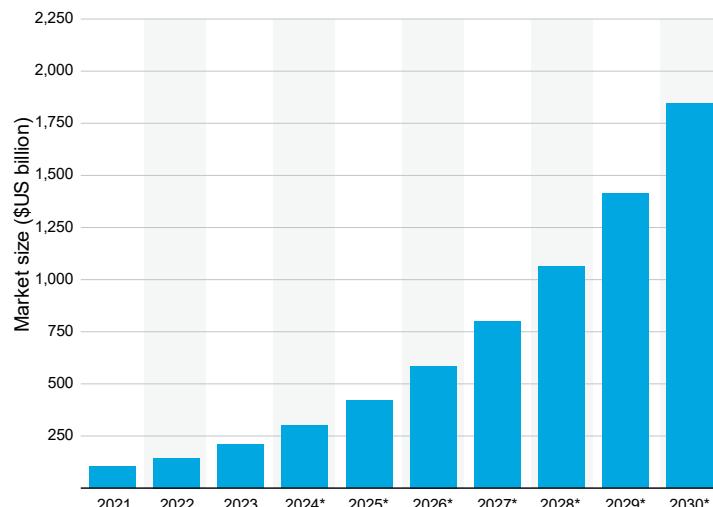

| Figure 44. Market growth worldwide for machine learning and artificial intelligence through 2030. ....                                      | 183 |

| Figure 45. Neural network with one hidden layer.....                                                                                        | 183 |

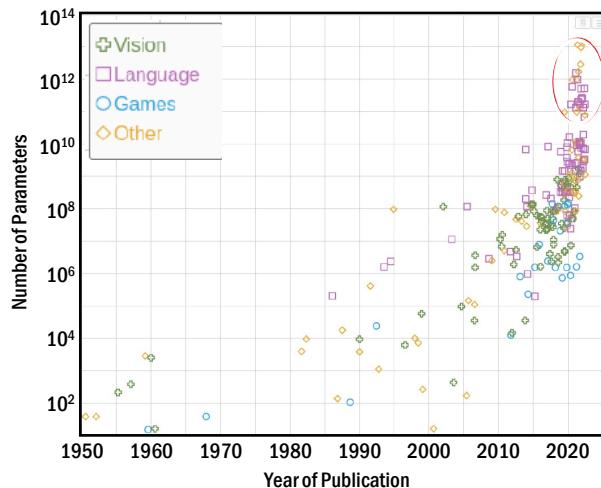

| Figure 46. Complexity of machine learning models.....                                                                                       | 185 |

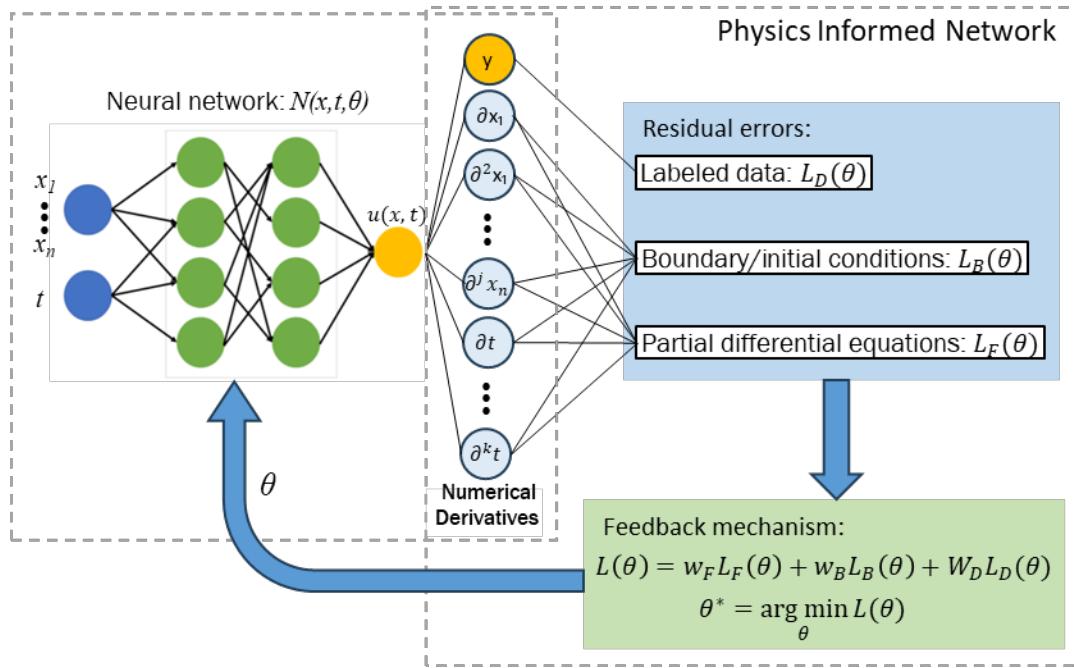

| Figure 47. Physics-informed neural network differential equation solver.....                                                                | 189 |

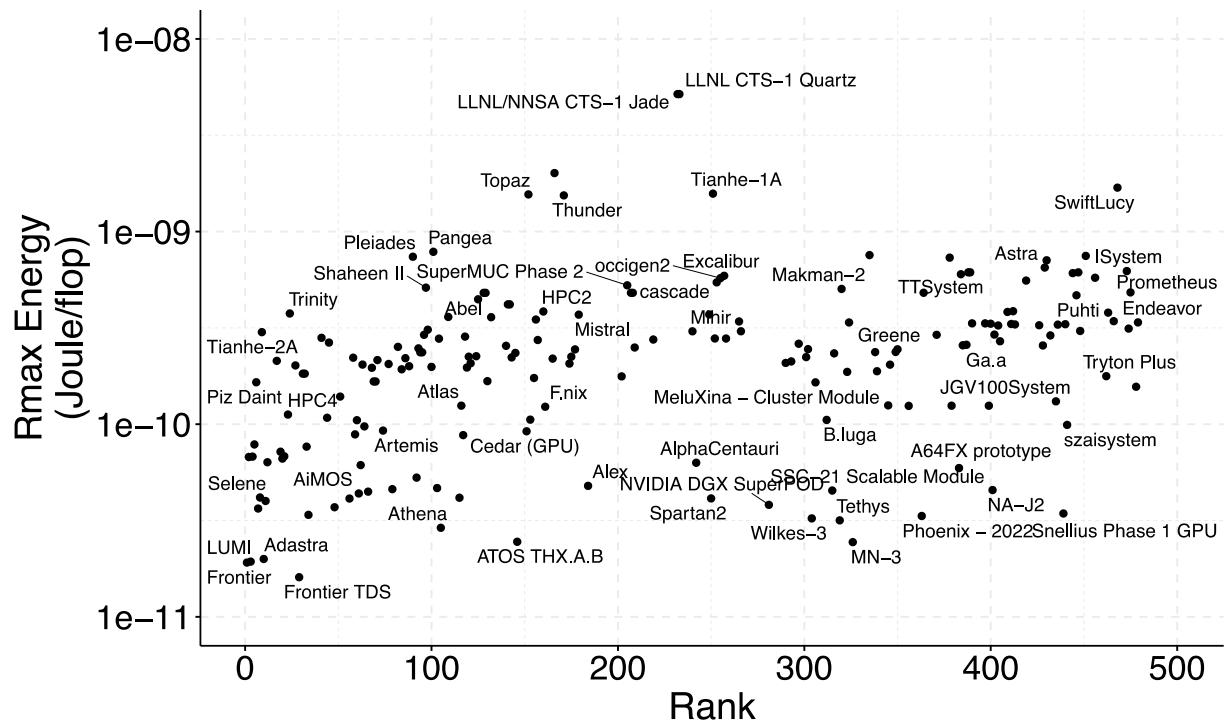

| Figure 48: Energy/Instruction based on HPL benchmarks Rmax.....                                                                             | 193 |

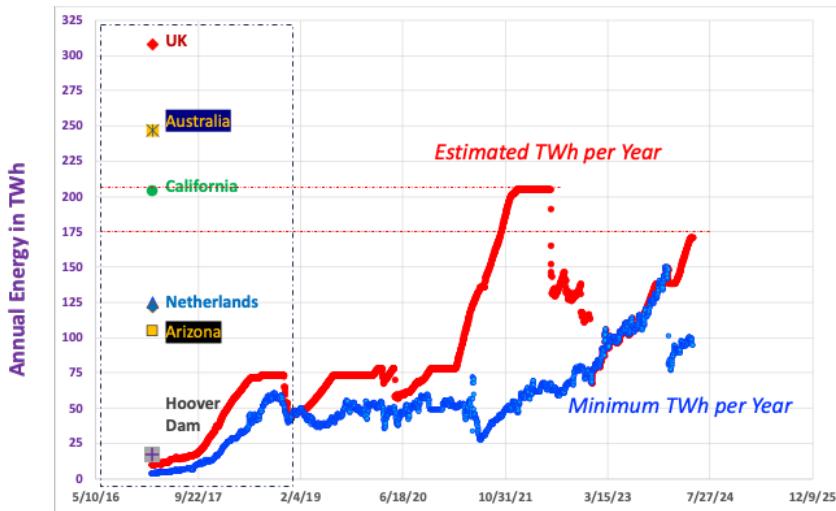

| Figure 49. Energy use estimates of cryptocurrency mining. ....                                                                              | 194 |

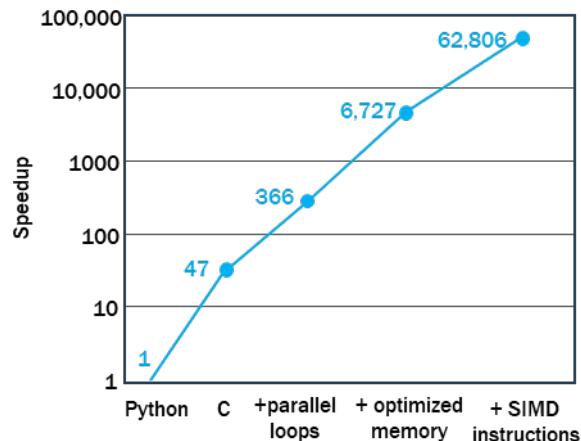

| Figure 50. Matrix multiplication speedup over native Python.....                                                                            | 197 |

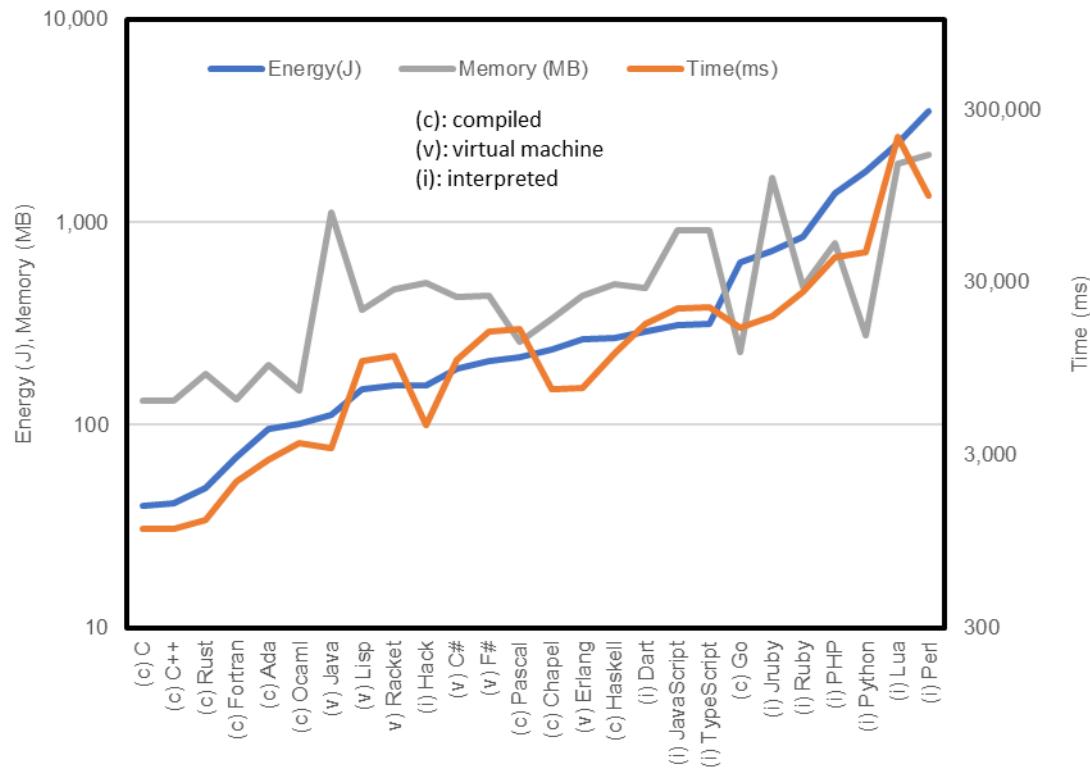

| Figure 51. Comparison of the energy, speed, and memory used for various programming languages. ....                                         | 198 |

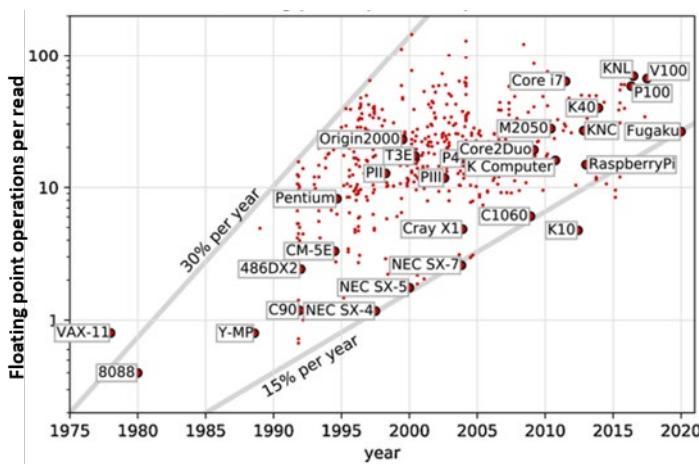

| Figure 52. Growing machine imbalance over time.....                                                                                         | 205 |

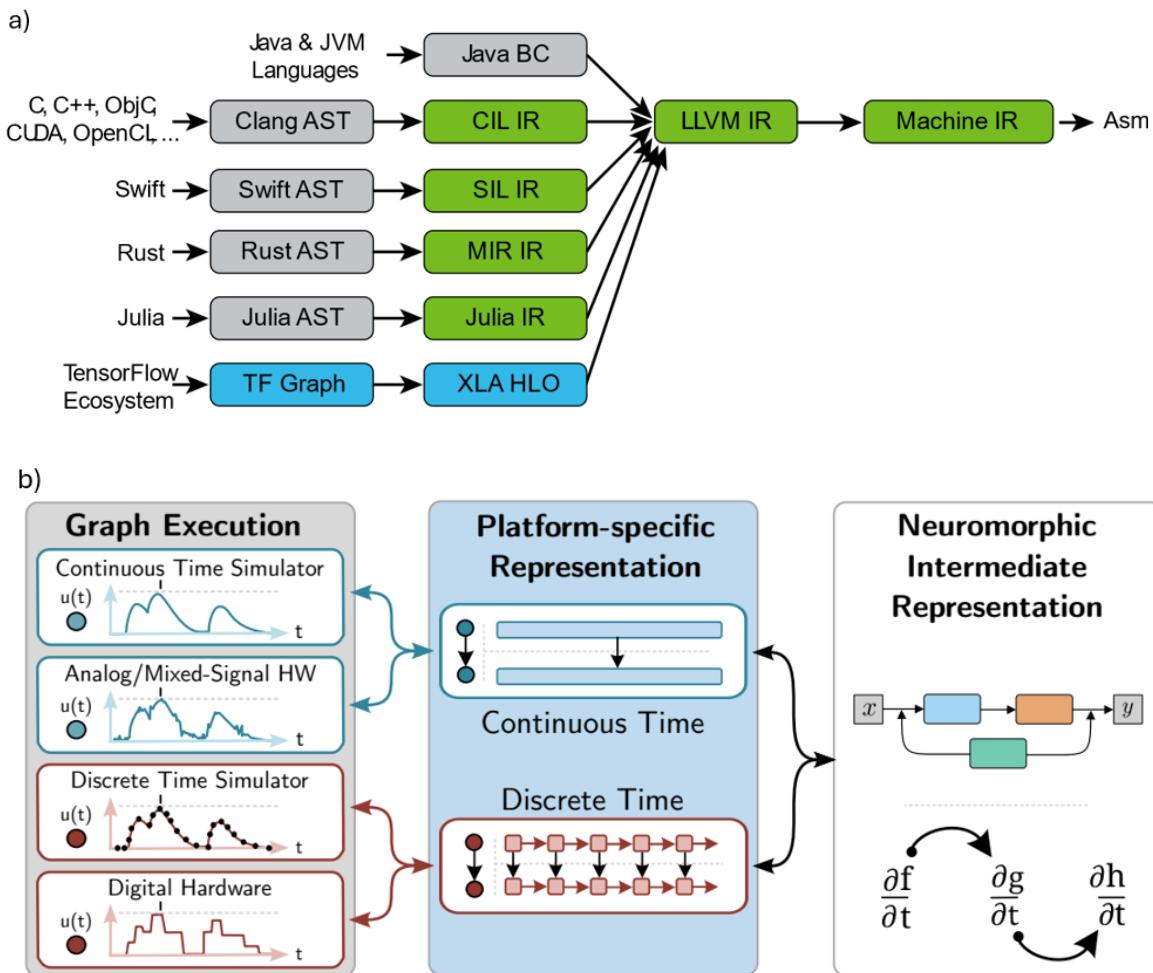

| Figure 53. Neuromorphic intermediate representation. ....                                                                                   | 207 |

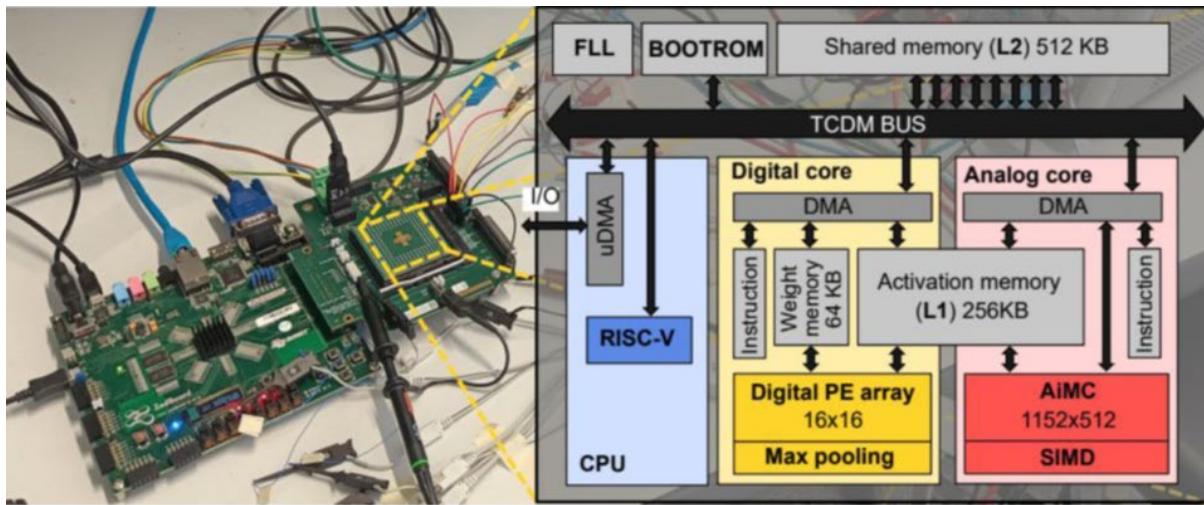

| Figure 54. An example neuromorphic computer architecture with embedded RISC-V processor. ....                                               | 208 |

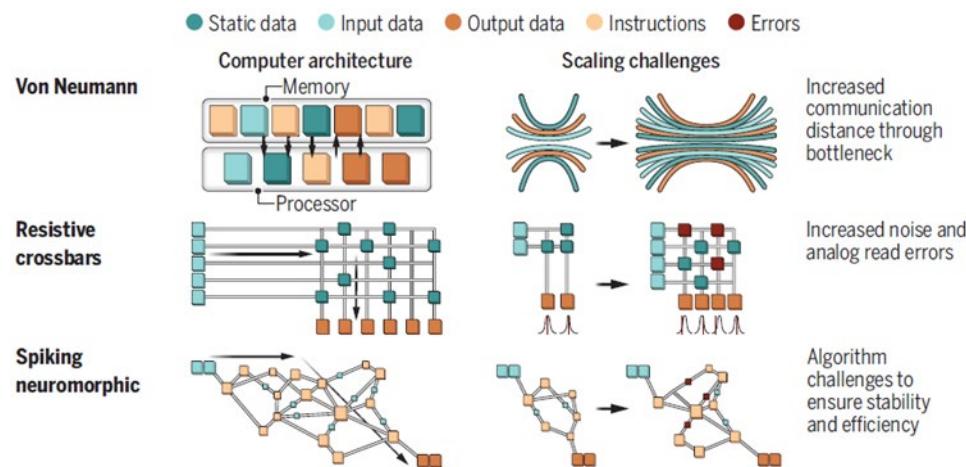

| Figure 55. Von Neumann, resistive crossbar, and spiking neuromorphic architecture paradigms and challenges.....                             | 209 |

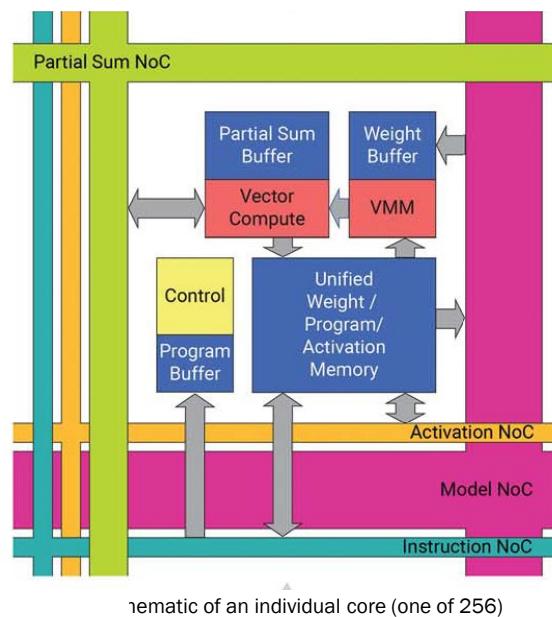

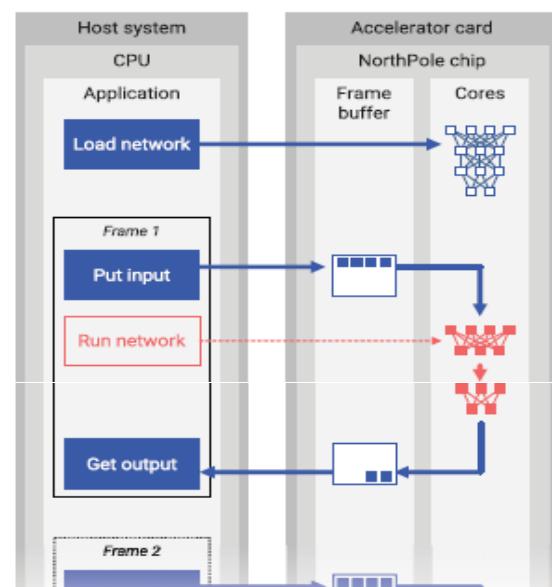

| Figure 56. IBM NorthPole digital neuromorphic chip. ....                                                                                    | 210 |

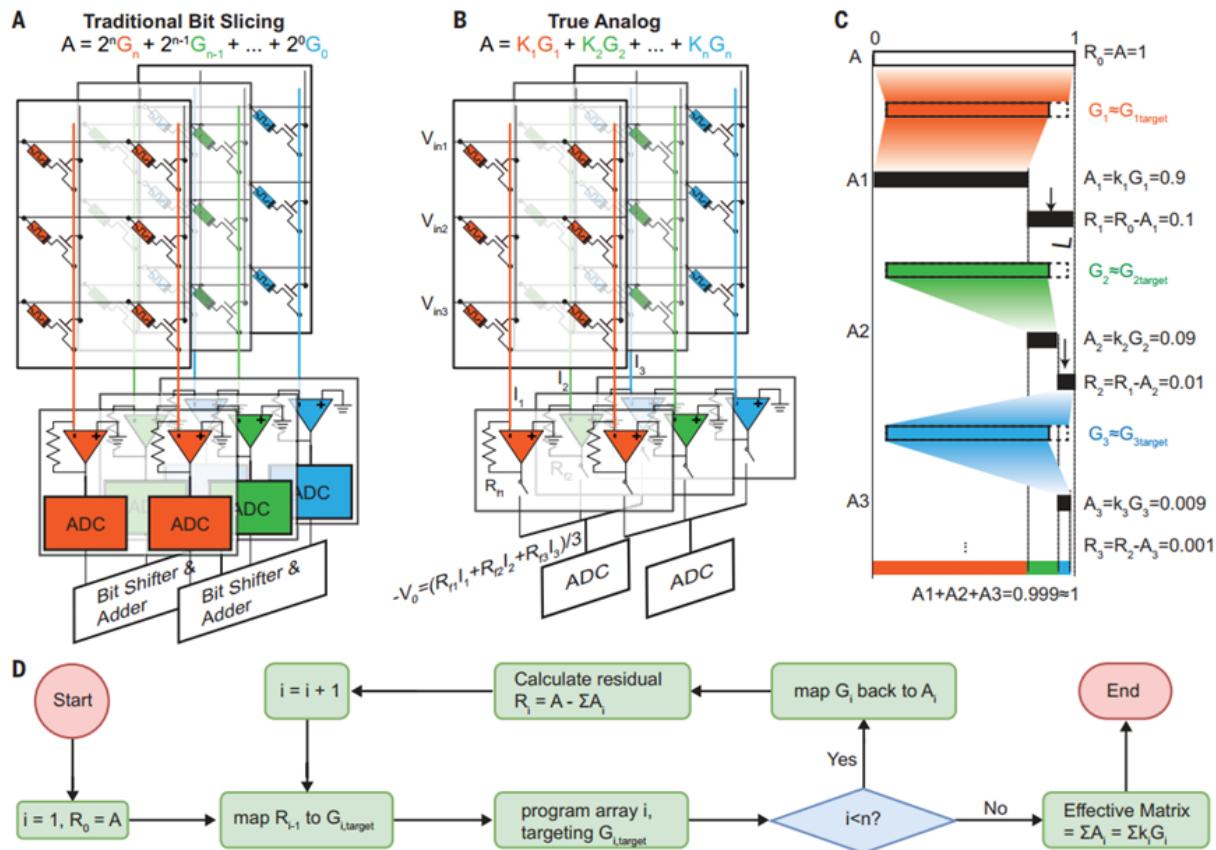

| Figure 57. Architecture and algorithm to achieve arbitrarily high precision with analog crossbar multipliers.....                           | 211 |

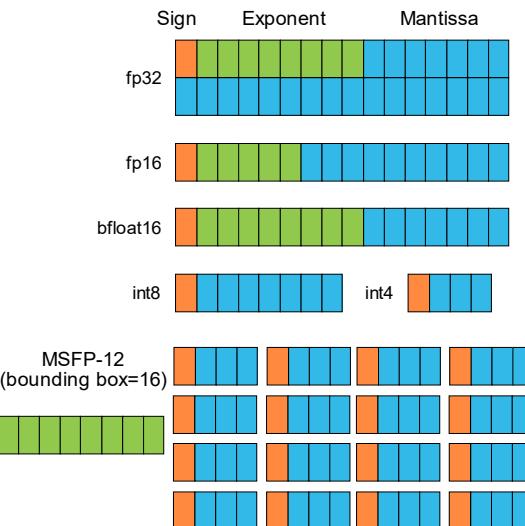

| Figure 58. Integer and floating-point numeric representations. ....                                                                         | 214 |

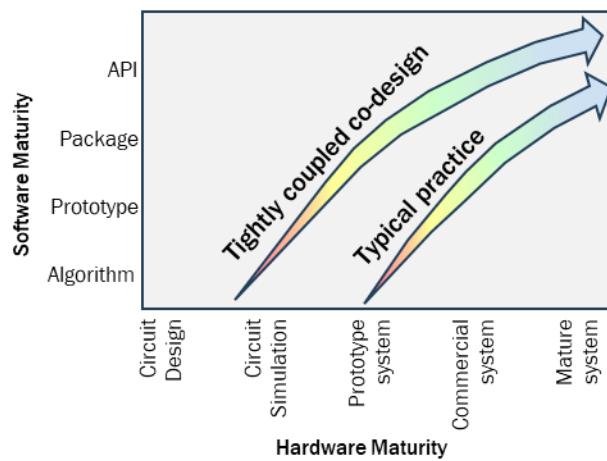

| Figure 59. Early engagement between hardware and software designers yields better software sooner. ....                                     | 215 |

| Figure 60. Potential efficiency improvement factor vs. timeline for PACE technologies. ....                                                 | 229 |

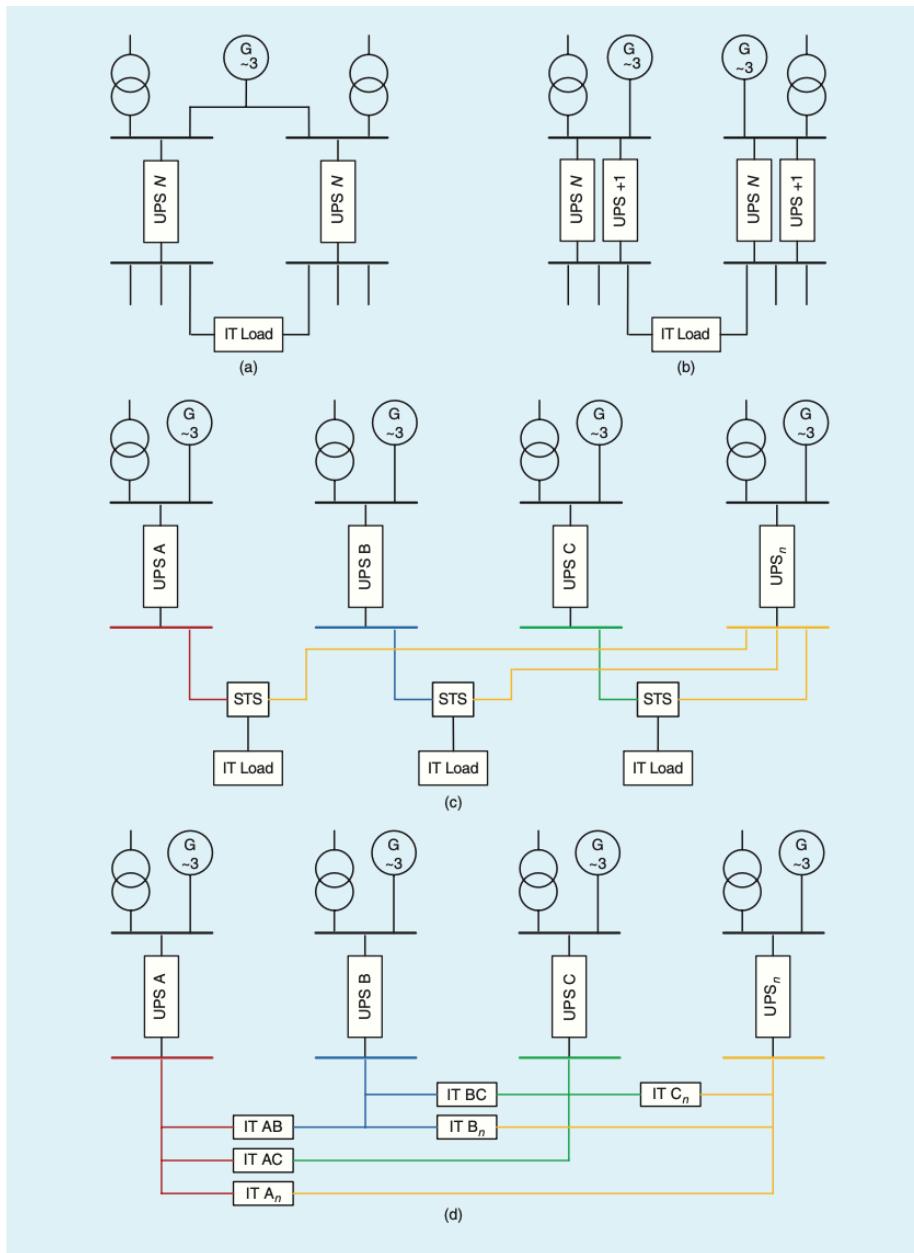

| Figure 61. Common power distribution architectures for data centers. ....                                                                   | 232 |

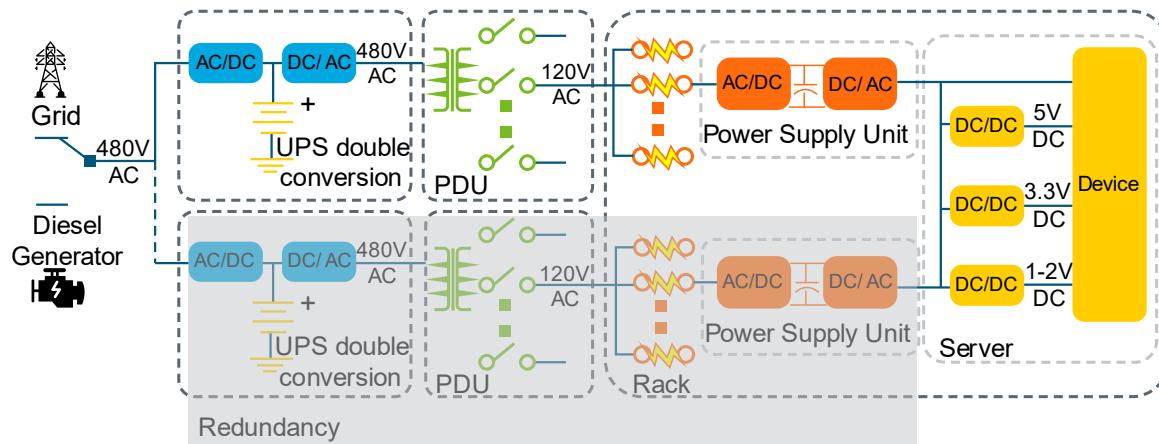

| Figure 62. Power electronics in the data center power delivery chain. ....                                                                  | 233 |

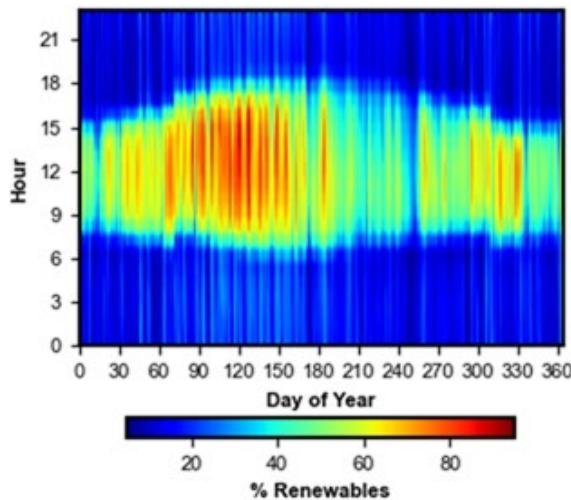

| Figure 63. Daily and hourly fraction of renewable energy in the California grid for 2022.....                                               | 236 |

|                                                                                                                    |     |

|--------------------------------------------------------------------------------------------------------------------|-----|

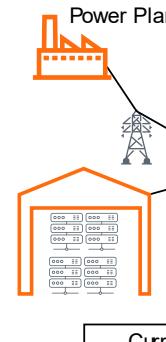

| Figure 64. Google carbon-intelligent compute management data center scheduling system concept .....                | 237 |

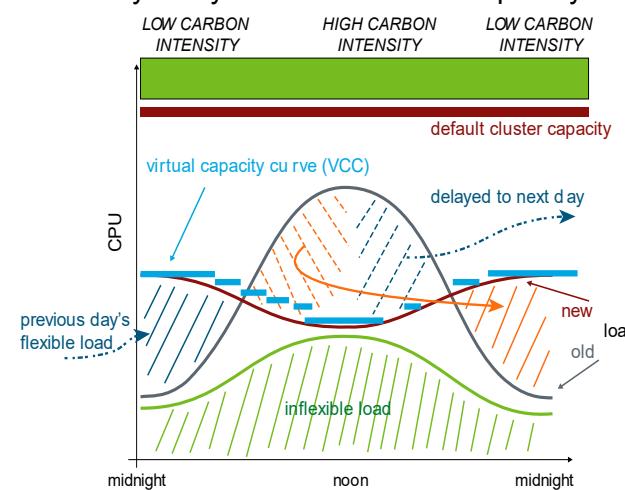

| Figure 65. “Virtual battery” shifts workload between data centers in response to renewable power availability..... | 237 |

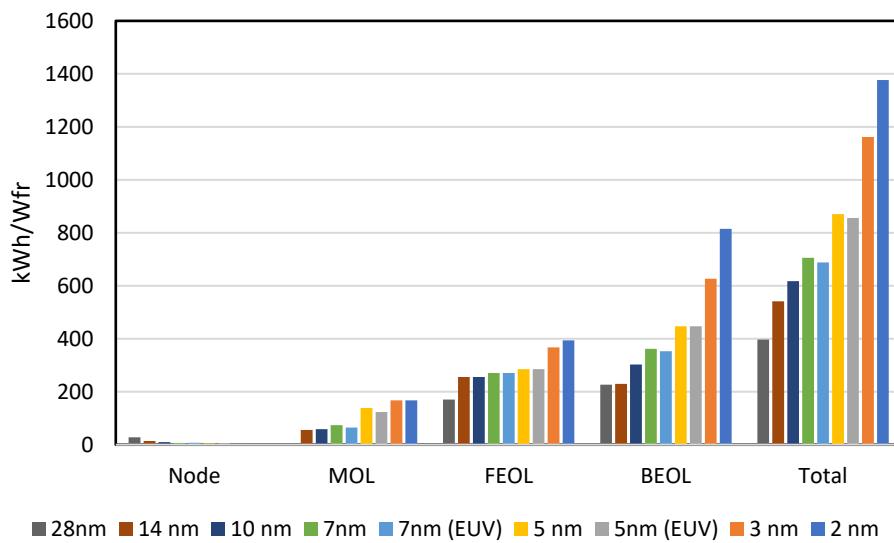

| Figure 66. Manufacturing energy costs per wafer for different technology nodes. ....                               | 251 |

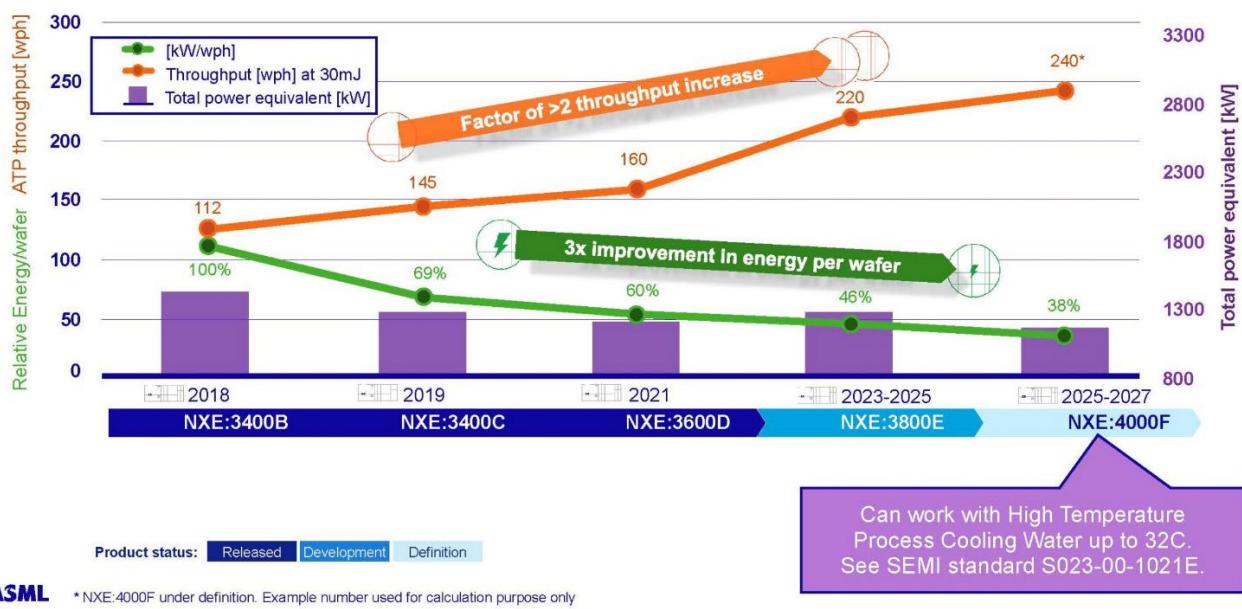

| Figure 67. Roadmap of EUV lithography tool developed by ASML. ....                                                 | 257 |

| Figure 68. Photolithography vs. nanoimprint lithography processes. ....                                            | 258 |

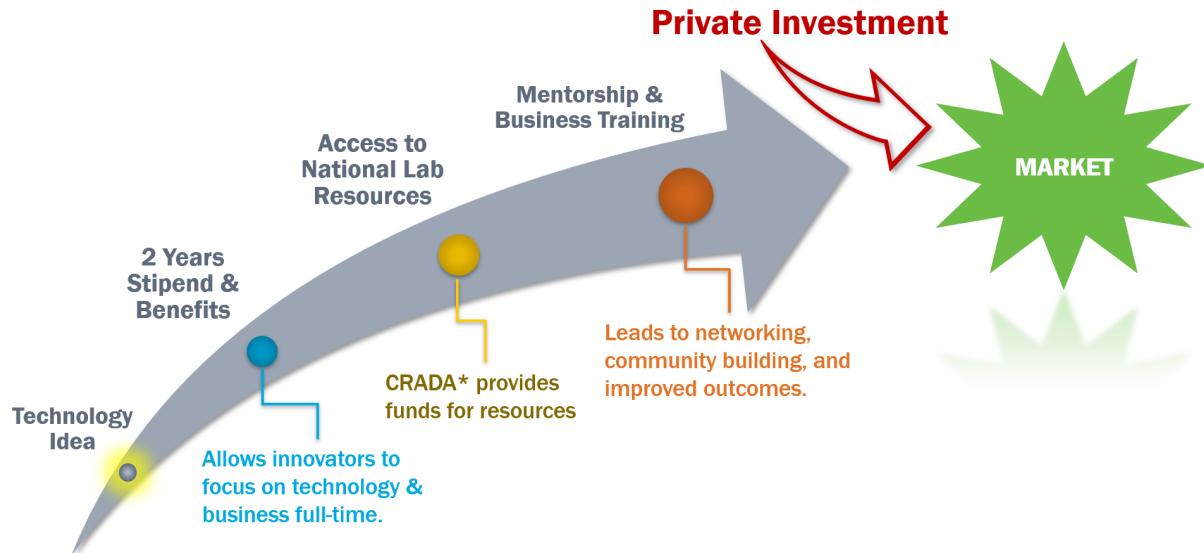

| Figure 69. LEEP brings technology idea to market-ready solutions. ....                                             | 286 |

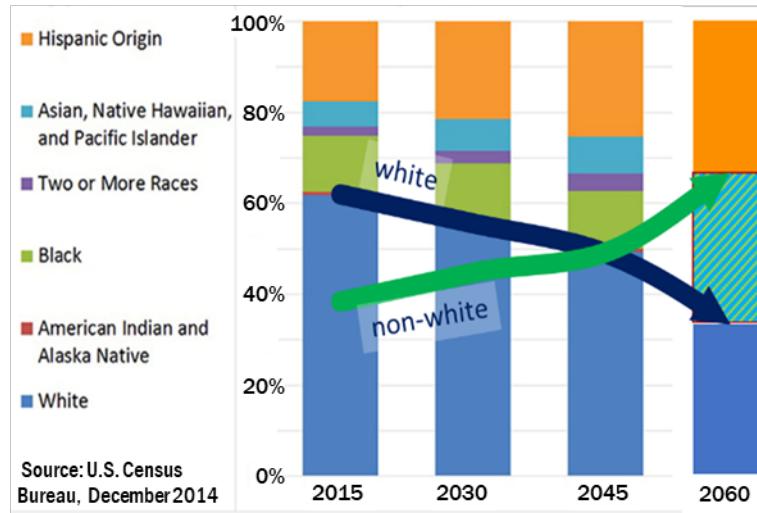

| Figure 70. STEM workforce diversity projection. ....                                                               | 293 |

| Figure 71. Top energy efficient technologies. ....                                                                 | 299 |

| Figure 72. Pledge signers for EES2 from September 2022– April 2024.....                                            | 300 |

## List of Tables

|                                                                                                                                              |       |

|----------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Table ES-1. Condensed Focus Areas for Energy Efficiency and their Manufacturing Challenges & Solutions <sup>a</sup> .....                    | xviii |

| Table ES-2. Condensed Focus Areas for Energy Efficiency and Their Grand Challenges and Solutions <sup>a</sup> .....                          | xix   |

| Table 1. 20 Years of Biennial Energy Efficiency Doubling .....                                                                               | 2     |

| Table 2. Workshop Series Used to Establish the Targeted Technologies and Associated Solution Pathways and Action Plans for the Roadmap ..... | 17    |

| Table 3. Promising Energy-Efficient Materials and Device Technologies.....                                                                   | 25    |

| Table 4. Key Takeaways for Energy Efficiency Opportunities in Materials and Devices .....                                                    | 26    |

| Table 5. Action Plan for 2D Semiconductor Materials .....                                                                                    | 32    |

| Table 6. Energy Impact and Timeline Estimates for Carbon Nanotube Field-Effect Transistors                                                   | 34    |

| Table 7. Action Plan for Carbon Nanotube Field-Efficient Transistors.....                                                                    | 37    |

| Table 8. Energy Impact and Timeline Estimates <sup>a</sup> for Carbon Nanotube Memory .....                                                  | 39    |

| Table 9. Action Plan for Carbon Nanotube Memory .....                                                                                        | 39    |

| Table 10. Energy Impact and Timeline Estimates <sup>a</sup> for Spintronic Logic .....                                                       | 42    |

| Table 11. Action Plan for Spintronic Logic .....                                                                                             | 44    |

| Table 12. Energy Impact and Timeline Estimates for Spintronic Memory .....                                                                   | 45    |

| Table 13. Action Plan for Spintronic Memory.....                                                                                             | 47    |

| Table 14. Energy Impact and Timeline Estimates <sup>a</sup> for FeFETs .....                                                                 | 49    |

| Table 15. Action Plan for Ferroelectric Memory/FeFETs. ....                                                                                  | 53    |

| Table 16. Energy Impact and Timeline Estimates <sup>a</sup> for TFETs .....                                                                  | 56    |

| Table 17. Action Plan for TFETs.....                                                                                                         | 59    |

| Table 18. Energy Impact and Timeline Estimates <sup>a</sup> for Si-GAA.....                                                                  | 61    |

| Table 19. Action Plan for Si-GAA.....                                                                                                        | 62    |

| Table 20. Device-Level Energy Impact and Timeline Estimates <sup>a</sup> for Analog Devices for Neuromorphic Computing. ....                 | 65    |

| Table 21. Action Plan for Emerging Devices and Materials for Analog Computing .....                                                          | 66    |

| Table 22. Important Properties for Materials in Low-k Applications <sup>a</sup> .....                                                        | 68    |

| Table 23. Dielectric Constants of Various Contemporary Low-k Materials <sup>a</sup> .....                                                    | 68    |

| Table 24. Action Plan for Interlayer Dielectrics .....                                                                                       | 69    |

|                                                                                                                                                                                  |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 25. Action Plan for Novel Interconnects .....                                                                                                                              | 71  |

| Table 26. Action Plan for Novel Contacts .....                                                                                                                                   | 73  |

| Table 27. Technology Groups Addressed by the Circuits and Architectures Working Group .....                                                                                      | 90  |

| Table 28. Key Takeaways for Energy Efficiency Opportunities in Circuits and Architectures .....                                                                                  | 91  |

| Table 29. CXL and UCle Energy Impact Factor Comparison and Timeline for Improvements to Memory Access .....                                                                      | 94  |

| Table 30. Action Plan for Memory Access .....                                                                                                                                    | 96  |

| Table 31. Action Plan for Interconnect Fabrics .....                                                                                                                             | 99  |

| Table 32. Comparison of SRAM-Based CIM at 1-Bit Precision .....                                                                                                                  | 101 |

| Table 33. Action Plan for Digital CIM .....                                                                                                                                      | 103 |

| Table 34. Neuromorphic CIM Technologies Compared to Current Commercial AI Accelerators at 1-Bit Precision .....                                                                  | 105 |

| Table 35. Action Plan for Analog CM/Neuromorphic Computing .....                                                                                                                 | 107 |

| Table 36. Comparison of Conventional Memory Architectures to Alternative Nonvolatile Memories .....                                                                              | 110 |

| Table 37. Energy Impact Factors of NVM Technologies Compared to DRAM and NAND .....                                                                                              | 111 |

| Table 38. Action Plan for Non-Volatile Memory .....                                                                                                                              | 112 |

| Table 39. Performance Comparison of Some Recent <sup>a</sup> Domain-Specific Architectures .....                                                                                 | 114 |

| Table 40. Action Plan for Domain-Specific Architectures .....                                                                                                                    | 115 |

| Table 41. Action Plan for Instruction Set Architectures .....                                                                                                                    | 117 |

| Table 42. Action Plan for Electronic Design Automation Improvements .....                                                                                                        | 121 |

| Table 43. APHI Technology Groups and Technologies of Interest .....                                                                                                              | 131 |

| Table 44. Key Takeaways for Energy Efficiency Opportunities in APHI .....                                                                                                        | 132 |

| Table 45. Comparison of Simulated Graphene Layers and Resistance, Capacitance, and Correlating Impact Factors of CNT Bundles Compared to Conventional Copper Interconnects ..... | 134 |

| Table 46. Action Plan for Carbon Nanotube-Based Interconnects .....                                                                                                              | 135 |

| Table 47. Action Plan for Optical Interconnects .....                                                                                                                            | 143 |

| Table 48. Impact and Timeline Estimates for 3D Hybrid Bonding .....                                                                                                              | 145 |

| Table 49. Action Plan for 3D Hybrid Bonding .....                                                                                                                                | 147 |

| Table 50. Energy Per Bit Comparisons of Different Vertical Integration Schemes .....                                                                                             | 151 |

| Table 51. Action Plan for Vertically Integrated Devices .....                                                                                                                    | 153 |

| Table 52. Action Plan for 3D Monolithic Integration .....                                                                                                                        | 155 |

| Table 53. Performance of Advanced Thermal Interface Materials Compared to Baseline Technologies .....                                                                            | 158 |

| Table 54. Action Plan for Thermal Interface Materials .....                                                                                                                      | 159 |